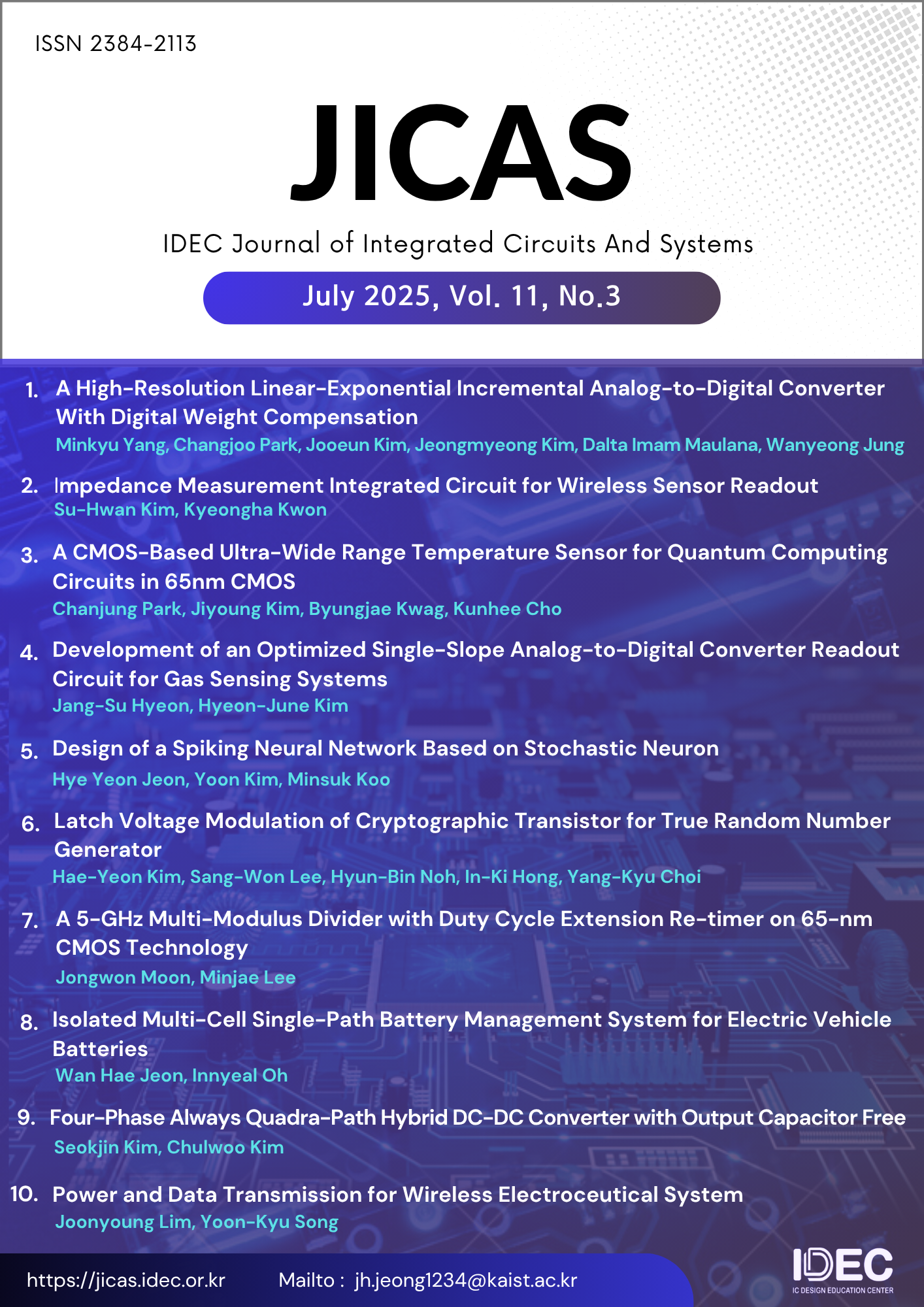

A 5-GHz Multi-Modulus Divider with Duty Cycle Extension Re-Timer on 65-nm CMOS Technology

Abstract

In this paper, a multi-modulus divider (MMD) operating at 5 GHz has been designed using a 65-nm CMOS process. The MMD core is composed of cascaded DIV2/3 cells. The first three stages were composed of TSPC D-flipflop, and the last stage was composed of static D-flipflop. We propose a re-timer that extends the duty cycle by generating an asynchronous reset through digital logic gates. This not only removes accumulated circuit noise, but also generates a duty cycle from at least 43% to 53% depending on the division ratio. Based on the output frequency of 200MHz, when N is 25, the total power consumption is 0.9mW, and the circuit size is 75μm*30.5μm.