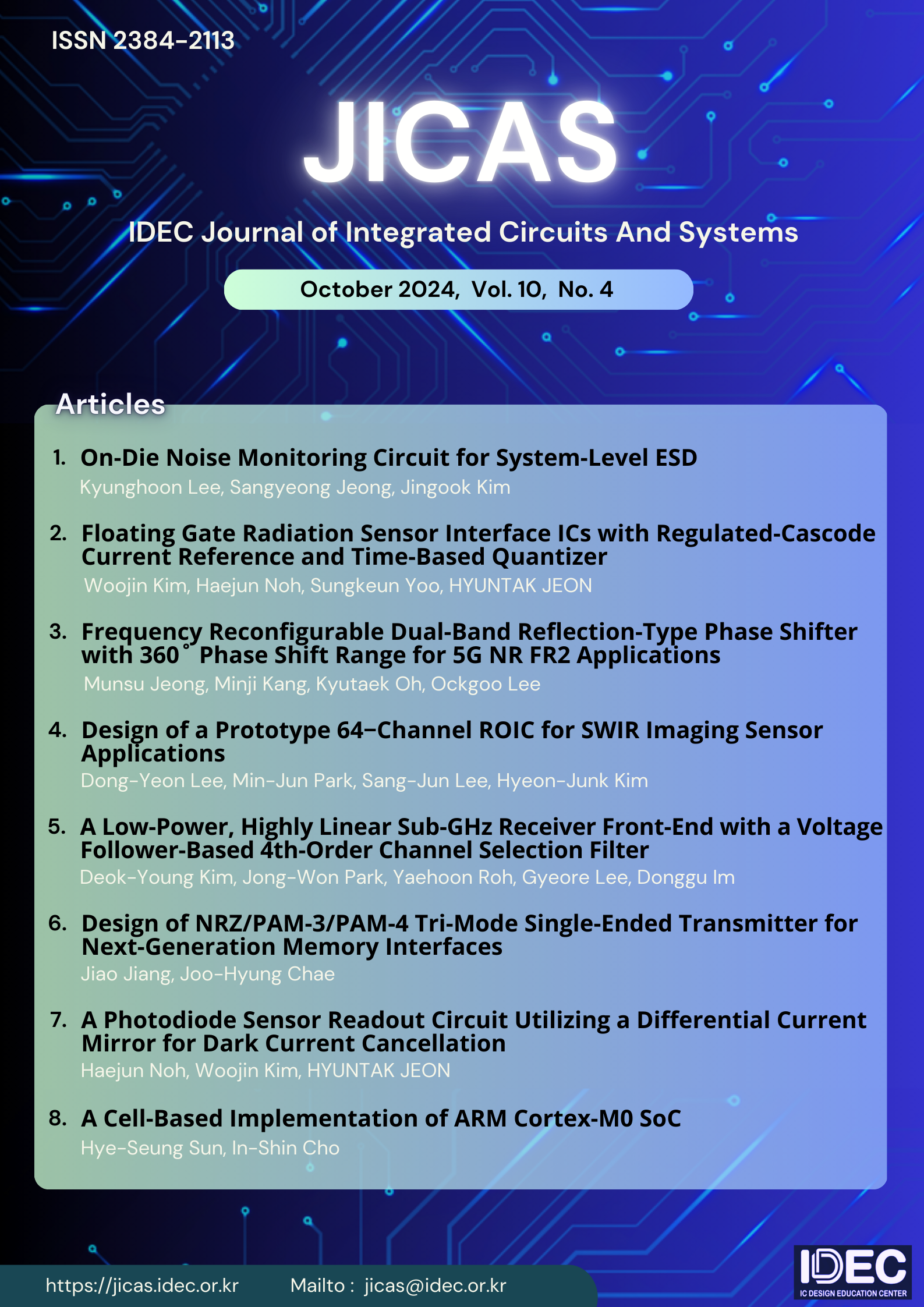

A Cell-Based Implementation of ARM Cortex-M0 SoC

Abstract

For academic research purposes, ARM provided the Cortex SoC platforms. This study presents the methods and results of implementing the Cortex-M0 as a chip. The behavioral memory was replaced with the Samsung memory, and the design was modified to allow software to be written externally to the chip at any time. Efforts were made to fully utilize as many EDA tools as possible during the chip implementation to maximize the chip's functionality and performance. The fabricated Cortex-M0 chip was mounted on a test board and was verified to work well in conjunction with the software. A hierarchical approach was adopted during the chip implementation, with efforts made to minimize its size and facilitate its use as a platform. In this study, the Samsung 28nm LPP process was applied.