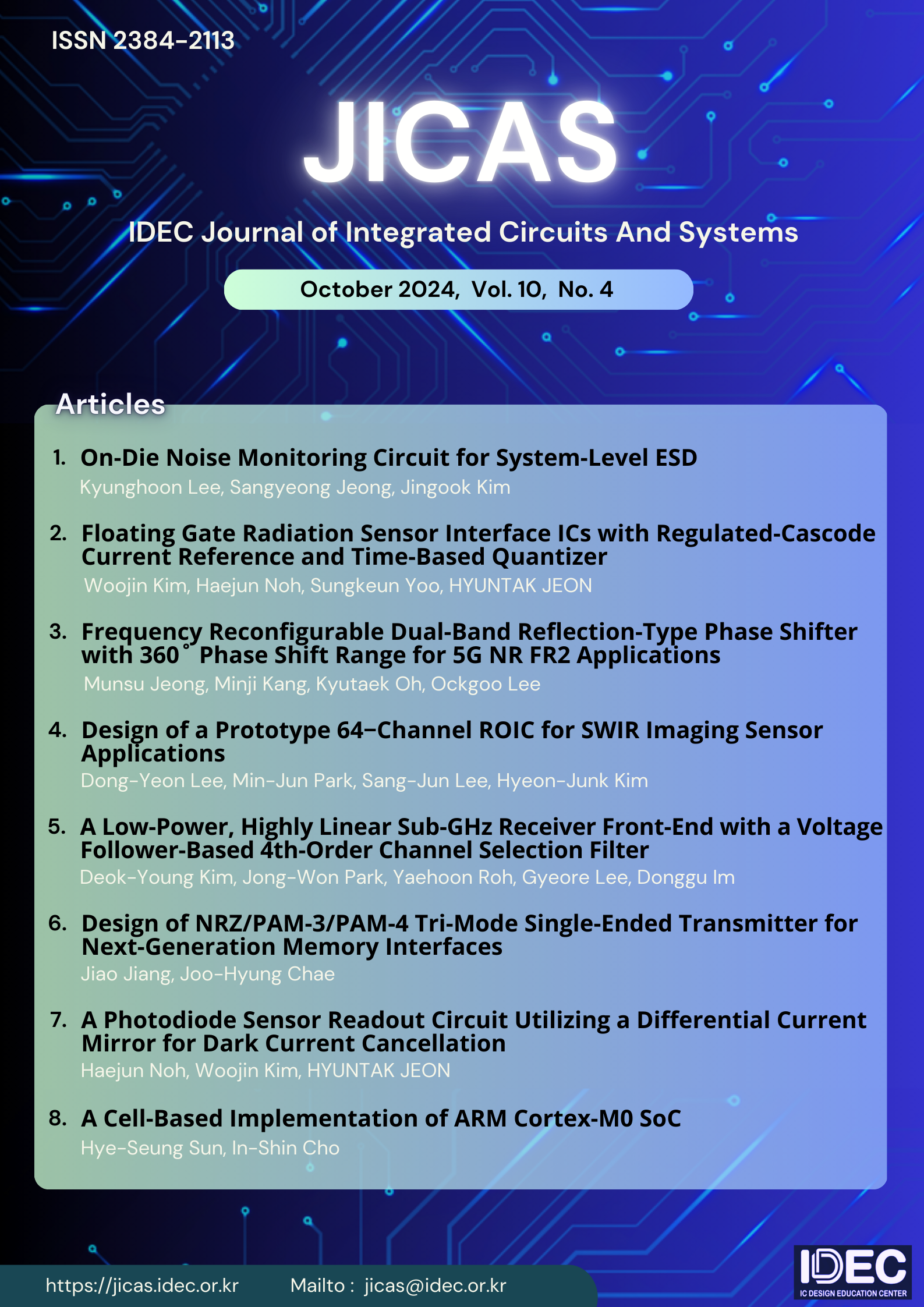

Design of a Prototype 64−Channel ROIC for SWIR Imaging Sensor Applications

Abstract

This paper presents the design and validation of a 64-channel prototype Readout Integrated Circuit (ROIC) forInGaAs-based compound semiconductor pixels, specificallyaimed at Short-Wave Infrared (SWIR) imaging systems. TheROIC, fabricated using a 0.18μm CMOS process, Consists of a64-channel array with a pitch of 50μm and a total chip area of5 × 2.5 mm². Comprehensive silicon-level validation has beenperformed to ensure stability and performance reliability. TheROIC achieves a random noise level of 119.48 μVrms andoperates with a total power consumption of 22.55 mW,demonstrating its suitability for infrared imaging applications.The study highlights the innovative approach of incorporatingvariable conversion gain and sensitivity adjustment toaccommodate different pixel signal characteristics, therebyenhancing the overall imaging performance.