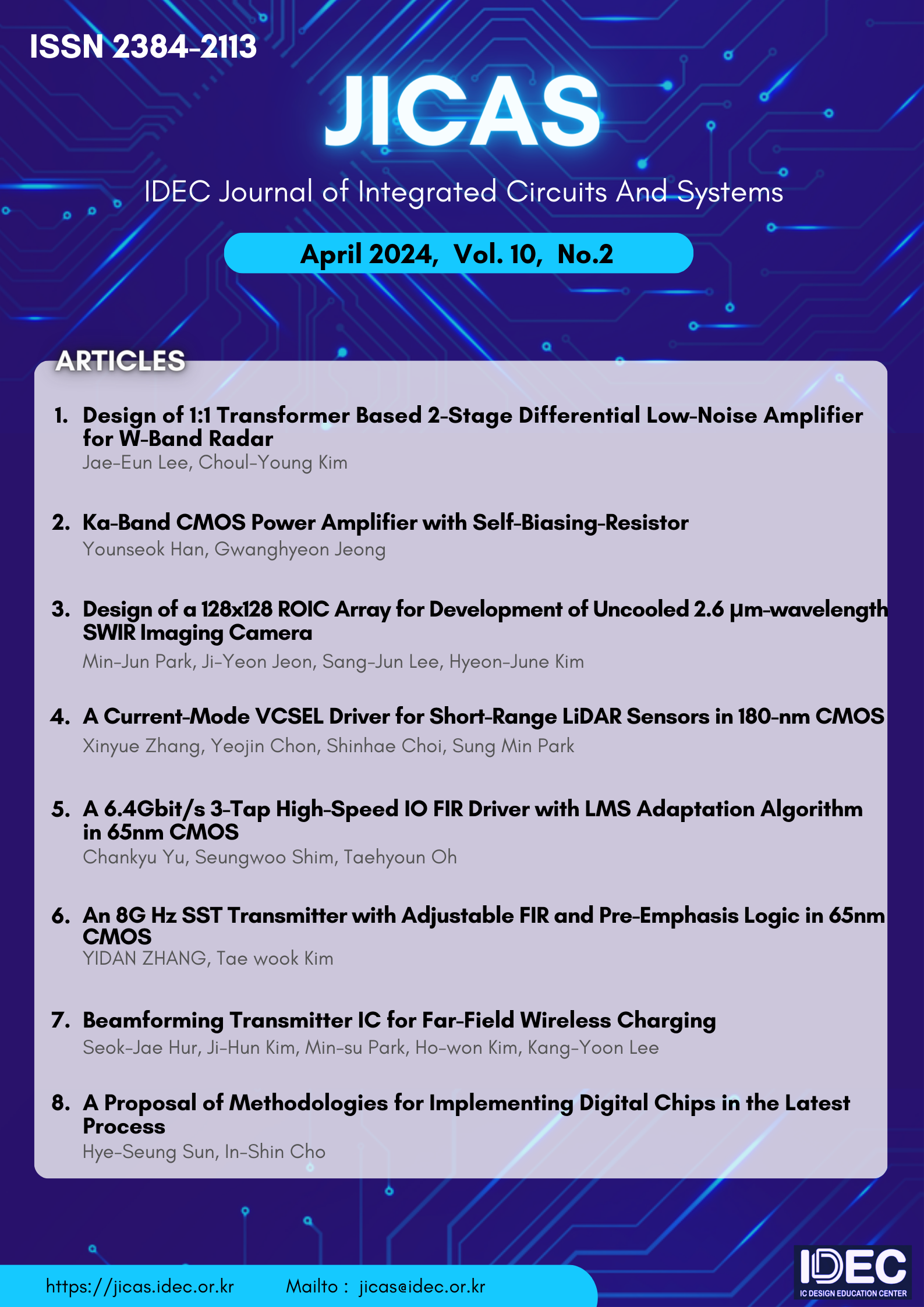

A 6.4Gbit/s 3-Tap High-Speed IO FIR Driver with LMS Adaptation Algorithm in 65nm CMOS

Keywords:

High-Speed IO, SerDes, Transceiver, FIR, Driver, variable gain amplifier, sigh-sign LMS

Abstract

A 6.4Gb/s IO transceiver including an adaptive finite impulse response (FIR) filter has been implemented with 65nm technology. The FIR tap coefficients are adapted using sign-sign least mean square (LMS) algorithm. Eye-openings are improved under time varying conditions by creating a diverse channel loss environment. The transceiver consumes 64mW/lane at 1.2V supply and the chip size is 0.506 mm2. The measured vertical eye-opening has been improved from 152.4mV/1.06V to 356.6mV/699.3mV after pre-emphasis and the measured horizontal eye-opening is 0.484 UI at 10-9 BER.

Published

2024-04-01

How to Cite

Yu, C., Shim, S., & Oh, T. (2024). A 6.4Gbit/s 3-Tap High-Speed IO FIR Driver with LMS Adaptation Algorithm in 65nm CMOS . Journal of Integrated Circuits and Systems, 10(2), 22-28. https://doi.org/10.23075/jicas.2024.10.2.005

Section

Articles