# Temperature-Independent Current Reference with Tunable Temperature Coefficient DAC

# Dabin Hong<sup>1</sup>, Pangi Park and SeongHwan Cho<sup>a</sup>

Department of Electrical Engineering, Korea Advanced Institute of Science and Technology E-mail: ¹dabinhong@kaist.ac.kr.

Abstract - Modern automobiles increasingly support a variety of advanced features, with autonomous vehicle safety gaining heightened attention. This has created a growing demand for sensor technology that can accurately detect environmental changes. One of the critical challenges in automotive sensor technology is the need for a temperature-compensated reference. This paper focuses on designing a temperatureindependent reference current source in this MPW. Conventional reference current sources are highly sensitive to environmental conditions, especially temperature fluctuations, leading to varying output values. Although several temperature-compensated reference current sources have been developed, effectively addressing the residual temperature coefficient resulting from process variations remains a challenge. To tackle this issue, we propose a circuit that compensates for residual temperature coefficients, enabling the creation of a stable, temperature-independent reference current source. This design aims to provide a reliable solution for the automotive sensor technology field, where maintaining accuracy across a range of environmental conditions is essential.

*Keywords*—Current reference, Temperature compensation, Temperature coefficient, Tunable DAC, PVT-insensitive

#### I. INTRODUCTION

As automobiles integrate more features and focus on safety increases, especially in autonomous vehicles, the demand for highly accurate sensor technology that remains reliable despite environmental changes is becoming increasingly important. While sensor accuracy is influenced by various factors, it fundamentally depends on a reference value, meaning the performance of the sensor is closely tied to the accuracy of the circuit providing this reference. These circuits include reference voltage sources, reference current sources, and reference frequency generators, with the sensor output indicating how much the input has deviated from these reference values. Despite the significant role this field plays, reference current sources have historically been more limited in circuit design options compared to reference

a. Corresponding author; chosta@kaist.ac.kr

Manuscript Received May 26, 2025, Revised Aug. 28, 2025, Accepted Aug. 29, 2025

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<a href="http://creativecommons.org/licenses/by-nc/4.0">http://creativecommons.org/licenses/by-nc/4.0</a>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

voltage sources, which are commonly used in analog-todigital converters (ADCs), or reference frequency generators, which serve frequency synthesizers [1]. Reference current sources, however, offer versatility in applications like current biasing and current-based DACs. Recognizing the importance of developing a reference current source that functions independently of environmental conditions, we proposed such a system. Among environmental factors, temperature fluctuations are known to particularly impact reference current sources. This is because generating current involves converting voltage into current, and the physical properties of the components used in this process (such as MOSFETs and resistors) are highly sensitive to temperature changes. Consequently, if a reference current source without temperature compensation is used in sensor applications, the output may vary with ambient temperature changes, even if the actual input remains constant. Thus, it is critical to employ a temperature-compensated reference current source.

### II. CURRENT REFERENCE

The proposed architecture is an expansion of the process, voltage and temperature (PVT) insensitive current reference proposed in [2].

# A. PVT-Insensitive Current Reference

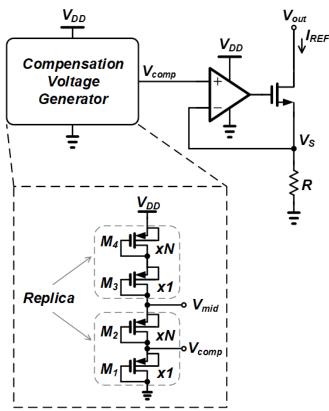

Fig. 1. shows the compensation voltage generator for current reference with process-insensitive temperature compensation [2]. This consists of a compensation voltage generator (CVG) and a current driver. The basic idea is to match the temperature coefficient (TC) of the resistance with the temperature coefficient of the compensation voltage  $V_{comp}$  to achieve a low TC.

The first-order temperature dependency of a resistor can be modeled as [3]

$$R(T) = R_0(1 + \alpha_{res}\Delta T) \tag{1}$$

where  $R_0$  is the value of resistance at nominal temperature  $T_0$  and  $\alpha_{res}$  is its first order TC, which remains unaffected by process variations.

The current of  $M_1$  and  $M_2$  operating in the subthreshold region is as

Fig. 1. PVT-insensitive current reference proposed in [2].

$$I_{M1} = \mu_p C_{OX} \frac{W}{L} V_T^2 \exp\left(\frac{V_{comp} - V_{TH1}}{m V_T}\right)$$

$$I_{M2} = \mu_p C_{OX} N \frac{W}{L} V_T^2 \exp\left(\frac{V_{mid} - V_{comp} - V_{TH2}}{m V_T}\right)$$

(2)

where  $\mu_p$  is the mobility of carrier,  $C_{OX}$  is the gate-oxide capacitance, W and L are the channel width and length, respectively, N is the size ratio of  $M_1$  and  $M_2$ , and  $V_{TH1}$  and  $V_{TH2}$  are the threshold voltages of  $M_1$  and  $M_2$ , respectively, and  $V_T$  is the thermal voltage, and m is the subthreshold slope factor.

Since  $I_{M1}$  and  $I_{M2}$  are equal,  $V_{comp}$  can be expressed as follow:

$$V_{comp} = \frac{V_{mid}}{2} + \frac{mV_{T}\ln(N)}{2} + \frac{\Delta V_{TH}}{2}$$

$$= \frac{V_{mid}}{2} + \frac{mkT_{0}\ln(N)}{2q} + \frac{\Delta V_{TH}}{2} + \frac{1}{2}\frac{mk}{q}\ln(N)\Delta T$$

$$= V_{comp0} \times \left(1 + \alpha_{comp}\Delta T\right) \qquad (3)$$

$$\alpha_{comp} = \frac{\frac{1}{2}\frac{mk}{q}\ln(N)}{\frac{1}{2}q} + \frac{mkT_{0}\ln(N)}{\frac{1}{2}q} + \frac{\Delta V_{TH}}{2} \qquad (4)$$

where  $V_{comp0} = \frac{V_{mid}}{2} + \frac{mkT_0\ln(N)}{2q} + \frac{\Delta V_{TH}}{2}$  and  $\alpha_{comp}$  is TC of CVG. If condition  $\frac{V_{mid}}{2} + \frac{\Delta V_{TH}}{2} \gg \frac{mkT_0\ln(N)}{2q}$  is met, TC of  $V_{comp}$  can be controlled by the size ration N which is sorely independent of process variation.

Based on the above results,  $I_{ref}$  shown in fig. 1. can be expressed as

$$I_{ref} = \frac{V_{comp0} \left(1 + \alpha_{comp} \Delta T\right)}{R_0 \left(1 + \alpha_{res} \Delta T\right)} = \frac{V_{comp0}}{R_0}$$

(5)

$I_{res}$  remains unaffected by temperature variations on condition  $\alpha_{comp} = \alpha_{res}$ .

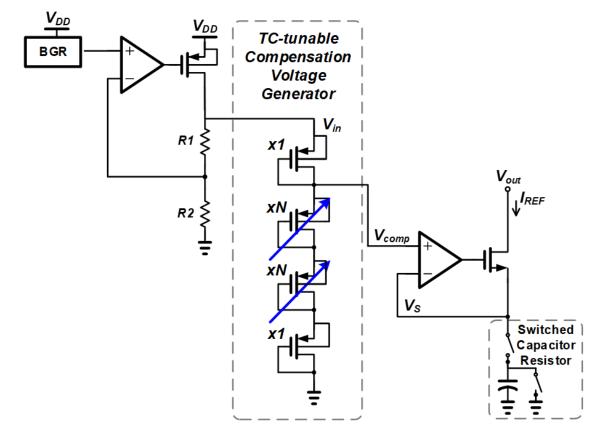

#### B. Proposed Current Reference

In order for the current reference from the previous section to achieve zero TC,  $\alpha_{comp}$  and  $\alpha_{res}$  must perfectly match. However, in practice, due to mismatches in size, threshold voltage, and subthreshold slope,  $\alpha_{comp}$  and  $\alpha_{res}$  may not match perfectly. Additionally, there is a dependency on the TC of the bandgap reference (BGR), which exhibits chip-to-chip variation, requiring a compensation circuit for the BGR's temperature dependency. To address these issues and enable compensation for the BGR's TC spread, we proposed TC-tunable current reference structure as shown in Fig. 2. This consists of a TC-tunable compensation voltage generator and a current driver.

Both the process variation of the TC for the poly resistor and the MIM capacitor are negligible; however, the resistance value of the poly resistor varies significantly with the process compared to the value of the MIM capacitance. Therefore, a switched capacitor-based resistor was used to improve the accuracy of the output current  $I_{ref}$ .

Through the same analysis as in the previous section,  $V_{comp}$  can be expressed as

$$V_{comp} = \frac{1}{2} \left( \frac{3V_{in}}{2} + \frac{mkT_0 \ln(N)}{q} + \Delta V_{TH} \right) + \frac{1}{2} \frac{mk}{q} \ln(N) \Delta T$$

(6)

where  $V_{IN}$  is the input voltage of the TC-DAC, m is the subthreshold slope factor, k is the Boltzmann constant, q is the electron charge, and N represents the W/L ratio of the PMOS in the TC-DAC.

The switched capacitor resistor can be modeled as [4]

$$R_{eq} = \frac{1}{Cf_{XO}} \tag{7}$$

where C is the capacitance and  $f_{XO}$  is the switching frequency. Then  $I_{ref}$  shown in Fig. 2. can be expressed as

$$I_{ref} = V_{comp} \cdot C \cdot f_{XO} \tag{8}$$

Fig. 2. Proposed temperature-compensated current reference with a tunable TC-DAC

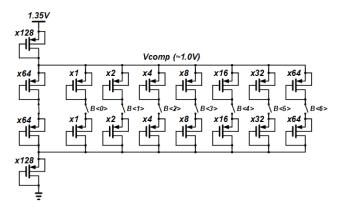

Fig 3. Proposed TC-DAC for post-cancellation of the residue temperature coefficient in the reference current after fabrication.

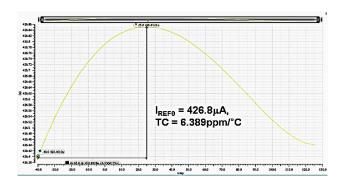

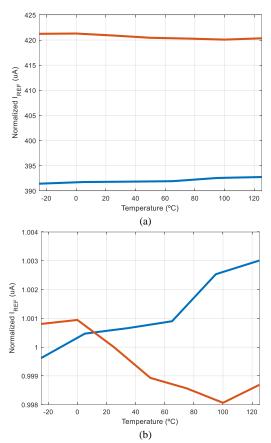

Fig 4. Simulated temperature independent current reference output versus temperature variation.

When using a crystal oscillator (XO) for the input frequency, its temperature coefficient is smaller than that of  $\mathcal{C}$  and  $V_{comp}$  (less than 1 ppm/°C), allowing the output current to be represented by the following equation.

$$I_{REF} = f_{XO} \cdot C_o (1 + \alpha_C \cdot \Delta T)$$

$$\times V_{comp0} (1 + \alpha_{comp}(N) \cdot \Delta T)$$

(9)

where  $\alpha_c$  is the TC of capacitor. Therefore, by adjusting the size ratio N to satisfy the following conditions, a zero TC current reference can be obtained.

$$\alpha_{comp}(N) = \alpha_C \tag{10}$$

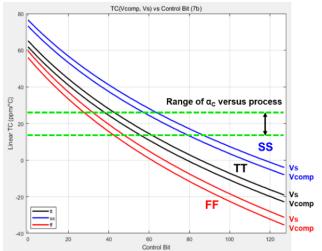

Due to non-idealities during chip fabrication, the temperature coefficient of the  $I_{ref}$  may not be completely eliminated. This residual TC is mainly caused by the variation in the TC of the BGR and the additional TC introduced by the offset of the op-amp used in the current driver. To further compensate for this, we proposed a TC-DAC structure as shown in Fig. 3, which allows for additional compensation of the residual TC caused by process variation. The proposed TC-DAC includes a 7-bit TC control for post-fabrication TC compensation. It is designed to cover the full temperature coefficient range of the MIM capacitor. As a result, the output current of the proposed reference current source with temperature

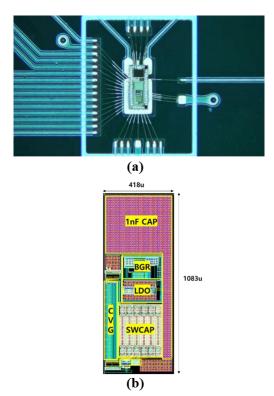

Fig 5. (a) Chip die photo after Chip-on-Board(COB), (b) Layout

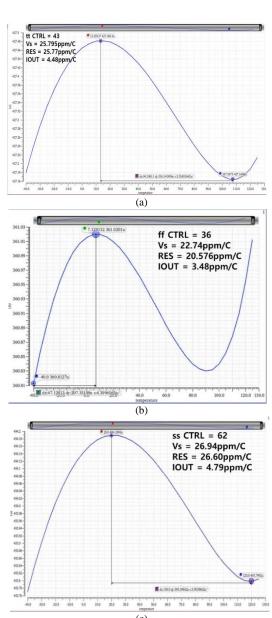

variation is shown in Fig. 4. The output value of the reference current source at the nominal corner is 426.8  $\mu A,$  with a TC of 6.389 ppm/°C across the automotive temperature range, demonstrating high thermal stability. Furthermore, even when residual temperature coefficients remain due to process variations, post-compensation can minimize the temperature coefficient.

# III. SIMULATION AND MEASUREMENT RESULTS

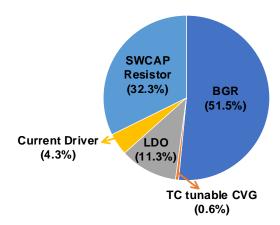

The proposed current reference is designed and fabricated in a 180-nm CMOS process. The die photo is shown in Fig. 5. At a supply voltage of 1.8V, the power consumption is 391.41 µW, with a detailed breakdown provided in Fig. 6. Most of the power consumption occurred in the BGR, and it is expected that power consumption can be reduced by adopting a different voltage reference structure. The proposed current reference was measured with the setup shown in Fig. 7. A function generator was used instead of a crystal oscillator, and  $I_{ref}$  was measured using a source meter over a temperature range of -25°C to 125°C. The simulation results for the proposed structure across different corners are shown in Fig. 8. As shown in Fig. 8, simulations confirmed that the controllable TC range of the proposed TC-DAC can cover the switched capacitor TC variation across all corners. Therefore, after fabrication, zero-TC can be achieved by matching the TC of the switched capacitor resistor and the CVG TC through foreground calibration.

The TC-DAC control code can be adjusted according to the process corner as shown in Fig. 9. The proposed structure can only cancel the first-order TC, leaving a second-order TC after compensation, which limits the ability to achieve perfect zero-TC.

Fig 6. Power breakdown

Fig 7. Measurement setup

Fig 8. Simulated TC of  $V_{comp}$  vs 7-bit control of proposed TC-DAC.

| Table                              | This<br>work | JSSC<br>2012[2] | ISSCC<br>2024[5] | TCAS-II<br>2020[6] | JSSC<br>2020[7] | ISSCC<br>2017[8] | CICC<br>2015[9] |

|------------------------------------|--------------|-----------------|------------------|--------------------|-----------------|------------------|-----------------|

| Technology(nm)                     | 180          | 180             | 180              | 180                | 180             | 180              | 180             |

| IREF                               | 406.24 uA    | 7.81 uA         | 10.9 uA          | 11.6 nA            | 1 nA            | 6.64 nA          | 10 uA           |

| Temperature Range( ${}^{\circ}$ C) | -25 to 125   | 0 to 100        | -20 to 125       | -40 to 120         | -20 to 80       | 0 to 110         | -40 to 80       |

| Avg. TC (ppm/ <sup>o</sup> C)      | 20.89        | 24.9            | 11.4             | 169                | 265             | 283              | 130             |

| Line<br>Sensitivity(%/V)           | *0.448       | 0.13            | 0.036            | 1.08               | 1.40            | 1.16             | 0.5             |

| Area(mm <sup>2</sup> )             | 0.2403       | 0.023           | 0.08             | 0.054              | 0.332           | 0.055            | 0.005           |

| Supply (V)                         | *1.7 to 2.4  | 1 to 1.2        | 1.3 to 2.4       | 0.8 to 2           | 1.5 to 2.0      | 1.3 to 1.8       | 2.4 to 3.0      |

<sup>\*</sup> Simulation

Fig 9. Simulation result of  $I_{ref}$  over process corners.

Fig 10. (a) Measured  $I_{REF}$  vs temperature variation (b) Normalized  $I_{ref}$  vs temperature variation.

To verify temperature stability, a temperature sweep was conducted, measuring the output current at  $25^{\circ}$ C intervals over a range from -25°C to  $125^{\circ}$ C while selecting the optimal code. A TC of 20.89 ppm/°C was achieved (Fig. 10).

The performance of the proposed current reference is summarized in Table I.

#### IV. CONCLUSION

In this paper, we have presented a design for a temperature-independent current reference with tunable temperature coefficient (TC) compensation. The proposed architecture addresses the challenges associated with process variations and residual temperature coefficients, which are critical issues in achieving reliable current sources in automotive sensor applications. Through the integration of a switched capacitor resistor and a TC-tunable compensation voltage generator, we successfully mitigated the effects of temperature fluctuations and process variations. The final design achieved a current reference with a temperature coefficient of 20.89 ppm/°C, demonstrating high thermal stability across a wide range of temperatures. This level of performance is well-suited for automotive and other highprecision applications where temperature independence is crucial. Future work may explore further optimization of the compensation techniques to enhance the robustness of the design under extreme environmental conditions.

#### ACKNOWLEDGMENT

This work was supported by the National Research Foundation of Korea(NRF) grant funded by the Korea government(MSIT)(RS-2024-00451169). fabrication and EDA tool were supported by the IC Design Education Center (IDEC), Korea.

#### REFERENCES

- [1] S. Lee and E. Sánchez-Sinencio, "Current reference circuits: A tutorial," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 68, no. 3, pp. 830-836, March 2021.

- [2] J. Lee, and S. Cho. "A 1.4-µW 24.9-ppm/° C current process-insensitive reference with temperature compensation in 0.18-µm CMOS," IEEE Journal of Solid-State Circuits., vol. 47, no. 10, pp.2527-2533, October 2012.

- [3] R. J. Baker, H. W. Li, and D. E. Boyce, CMOS Circuit Design, Layout, and Simulation, Revised, 2nd ed. New York: Wiley, 2008.

- [4] Razavi, Behzad, Design of Analog CMOS Integrated Circuits, McGraw-Hill, pp. 1-736, 2001.

- [5] Park, P., Lee, J., & Cho, S. (2024). A PVT-Insensitive Sub-Ranging Current Reference Achieving 11.4ppm/°C From -20°C to 125°C. IEEE Journal of Solid-State Circuits.

- [6] Huang, Q., Zhan, C., Wang, L., Li, Z., & Pan, Q. (2020). A-40° C to 120° C, 169 ppm/° C Nano-Ampere CMOS Current Reference. IEEE Transactions on Circuits and Systems II: Express Briefs, 67(9), 1494-1498.

- [7] Lee, S., Heinrich-Barna, S., Noh, K., Kunz, K., & Sánchez-Sinencio, E. (2020). A 1-nA 4.5-nW 289-ppm/° C current reference using automatic calibration. IEEE Journal of Solid-State Circuits, 55(9), 2498-2512.

- [8] Ji, Y., Jeon, C., Son, H., Kim, B., Park, H. J., & Sim, J. Y. (2017, February). 5.8 A 9.3 nW all-in-one bandgap voltage and current reference circuit. In 2017 IEEE

- International Solid-State Circuits Conference (ISSCC) (pp. 100-101). IEEE

- [9] Wu, C., Goh, W. L., Kok, C. L., Yang, W., & Siek, L. (2015, September). A low TC, supply independent and process compensated current reference. In 2015 IEEE Custom Integrated Circuits Conference (CICC) (pp. 1-4). IEEE.

management ICs.

Dabin Hong received the B.S. in electrical engineering from Ulsan National Institute of Science and Technology (UNIST), South Korea, in 2022. She is currently pursuing the integrated master's and doctoral degree in electrical engineering from Korea Advanced Institute of Science and Technology (KAIST), Daejeon,

South Korea. Her research interest includes battery

Pangi Park received the B.S. in biomedical engineering Hanyang University, Seoul, South Korea, in 2019. He is currently working toward the Ph.D. degree in electrical engineering from the Korea Advanced Institute of Science and Technology, Daejeon, South Korea. His current research interests include biomedical sensors, battery management ICs,

and current sensor interfaces.

**SeongHwan Cho** received the B.S. degree in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 1995, and the M.S. and Ph.D. degrees in EECS from MIT, Cambridge, MA, USA, in 1997 and 2002, respectively.

In 2002, he joined Engim, Inc. Acton, MA, USA, where he was involved in data converters and

phased-locked loop (PLL) design for IEEE 802.11abg WLANs. Since 2004, he has been with the School of EE, KAIST, where he is currently a Professor and the Department Head of semiconductor system engineering. He was with Marvell Inc., Santa Clara, CA, USA, from 2011 to 2012, and Google, London, U.K., from 2016 to 2017, as the Research Scientist. His research interests include analog and mixed-signal circuits for high-speed communication, lowpower sensors, memory, and machine learning.

Prof. Cho was a co-recipient of the 2009 IEEE Circuits and System Society Guillemin-Cauer Best Paper Award and the 2012 ISSCC Takuo Sugano Award for Outstanding Far-East Paper. He has twice received Outstanding Lecturer Award from KAIST. He has served on the Technical Program Committee on several IEEE conferences, including ISSCC, Symposium on VLSI and A-SSCC. He has served as an Associate Editor for IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS, and Distinguished Lecturer of the IEEE Solid-State Circuits Society.