## A Fast Adaptive and Fine Stabilizer Based Digital LDO

Ibrar Ali Wahla<sup>1</sup>, Muhammad Abrar Akram<sup>2</sup> and In-Chul Hwang<sup>a</sup>

<sup>1, a</sup> Department of Electrical and Electronics Engineering, Kangwon National University

<sup>2</sup>Department of Electrical Engineering, Qatar University, Doha, Qatar

$E\text{-mail: }^{1} Ibrarwhala@kangwon.ac.kr, ^{2}m.akram@qu.edu.qa$

Abstract - In this brief, a fully integrated digital low-dropout regulator (DLDO) is proposed to address the trade-offs between transient response and power efficiency in dynamic load conditions. The design features a fast-adaptive glitchdriven coarse loop controller, which rapidly adjusts PMOS switches using precisely generated pulses, minimizing transient recovery time (TREC) even during large load current (ILOAD) changes. Additionally, a fine voltage stabilizer ensures steadystate voltage stability by employing high-resolution PMOS control. The DLDO is fabricated in a 65-nm CMOS process, the proposed DLDO supports an input voltage range of 0.6 V to 1.2 V and achieves a regulated output voltage from 0.55 V to 1.15 V. Simulation results demonstrate a 264 mV voltage droop recovery within 19.11 ns for a 26 mA load step, achieving a figure-of-merit of 0.225 ns<sup>2</sup> and a peak current efficiency of 99.32%. The low quiescent current of 157 µA makes it highly suitable for power-efficient SoC applications requiring both fast transient response and precise voltage regulation.

*Keywords*— digital low-dropout regulator (DLDO), Fine voltage stabilizer, fast transient, Glitch-driven control

### I. INTRODUCTION

Low-dropout regulators (LDOs) are indispensable components in modern power management systems, ensuring stable power delivery for sensitive electronic applications [1]. They play a critical role in system-on-chip (SoC) platforms, which demand efficient point-of-load power delivery while adhering to strict integration and performance requirements. To meet these demands, LDOs must provide fast transient responses, maintain steady-state voltage stability, and operate within compact form factors compatible with advanced CMOS technologies. While conventional analog LDOs have served these purposes, their limitations in scalability and power efficiency under dynamic conditions have prompted a shift towards fully integrated digital LDOs (DLDOs) [2].

DLDOs offer several advantages over their analog counterparts, such as design simplicity, scalability, and compatibility with CMOS scaling trends. These attributes make them particularly attractive for applications ranging from microampere to sub-ampere load currents in both

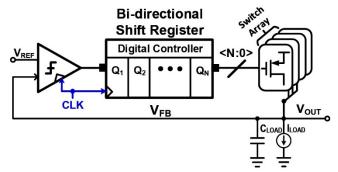

Fig. 1. Block diagram of the first implementation of a digital Low-Dropout Regulator (LDO)

consumer electronics and industrial systems [3]. However, existing DLDO architectures face significant challenges when deployed in dynamic load conditions. One of the primary issues is the trade-off between transient response and power efficiency [4], [5]. Conventional DLDO architectures, as illustrated in Fig. 1, rely heavily on clocked comparators and fixed-frequency controllers to regulate the output voltage, which introduces delays in transient response and increases quiescent current (I<sub>Q</sub>), especially during lowpower operation modes. These limitations make conventional designs unsuitable for advanced SoC platforms that demand both high performance and low energy consumption [6]–[8].

Several innovative approaches have been proposed to overcome these challenges. For example, Kang et al. introduced an event-driven DLDO architecture that eliminates clock dependencies, resulting in faster transient responses. However, this approach requires sophisticated event-detection mechanisms, which significantly increase circuit complexity and power overhead [9]. Similarly, Nasir et al. proposed a dual-loop control strategy consisting of a high-speed coarse loop to handle large load changes and a slower fine loop for steady-state adjustments. While effective, this method still depends on clocked control systems, which limit its responsiveness to highly dynamic load conditions [10]–[14]. These prior works highlight the critical need for DLDO designs that balance transient performance, power efficiency, and circuit simplicity.

In response to these challenges, this study proposes a glitch-driven coarse loop controller for coarse regulation in DLDOs. By leveraging precise glitch pulses generated from changes in the lock signal of the Voltage Range Detector, the proposed controller rapidly adjusts the state of PMOS switches.

a. Corresponding author; ihwang@kangwon.ac.kr

Manuscript Received Jan. 24, 2025, Revised Mar. 7, 2025, Accepted Mar. 11, 2025

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<u>http://creativecommons.org/licenses/by-nc/4.0</u>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

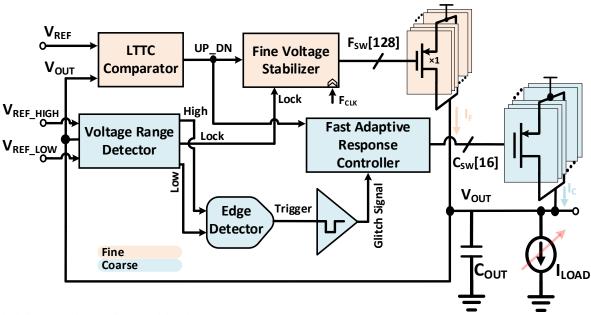

Fig. 2. Block diagram of the overall proposed digital LDO.

This mechanism significantly reduces the transient recovery time ( $T_{REC}$ ) of ( $V_{Droop}$ ), even during large ( $I_{LOAD}$ ) transients, and addresses the limitations of conventional clocked designs. Additionally, the integration of a dual-loop system, consisting of a coarse loop for rapid voltage adjustments and a fine-tuned loop for precise regulation, enables improved load transient response and recovery time.

The remainder of this article is structured as follows. Section II introduces the proposed digital low-dropout regulator (DLDO) architecture, detailing its overall block diagram and the functionality of the proposed blocks. Section III presents the simulation results, offering a detailed analysis of the key performance metrics, including transient recovery time, line regulation, and load transient response. Section IV concludes the paper by summarizing the key contributions of the proposed DLDO design and discussing its potential impact on power management for modern SoCs.

### II. DESIGN METHODOLOGY

### A. Overall Block Diagram

The proposed Digital Low-Dropout Regulator (DLDO) system, illustrated in Fig. 2, is designed to address dynamic voltage regulation challenges through an integrated framework of advanced control methodologies and circuit components. The architecture comprises a Logic Threshold Trigger Comparator (LTTC), Voltage Range Detector, Edge Detector, Glitch Generation Block, Fast-Adaptive Response Controller for coarse regulation, and a Fine Voltage Stabilizer. Each block is meticulously engineered to ensure a fast-transient response and precise voltage regulation, collectively contributing to a robust and energy-efficient power management solution.

The operation of the DLDO system is best understood through the accompanying timing diagram, which captures the transient response following a sudden change in load current ( $I_{LOAD}$ ). When ( $V_{OUT}$ ) drops below the lower

reference threshold ( $V_{REF\_LOW}$ ) due to an increased load, a voltage droop ( $V_{DROOP}$ ) occurs. The LTTC detects this deviation and generates a UP\_DN signal to indicate the need for corrective action. Simultaneously, the Voltage Range Detector identifies whether ( $V_{OUT}$ ) has crossed the predefined reference voltage range, triggering the Edge Detector, which subsequently generates a Trigger signal.

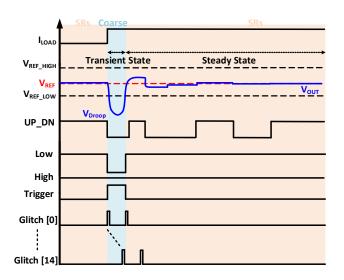

In response, the Glitch Generation Block produces precisely timed glitch pulses that activate the Fast-Adaptive Response Controller, initiating the coarse regulation loop. This loop dynamically engages multiple PMOS switches to restore ( $V_{OUT}$ ) to the desired level. As depicted in the Fig. 3, timing diagram, a sequence of glitch pulses is generated during the transient state, expediting the voltage correction process. Once ( $V_{OUT}$ ) stabilizes within the acceptable range, the system transitions to steady-state operation, where the Fine Voltage Stabilizer takes over, performing highprecision adjustments to maintain ( $V_{OUT}$ ) equal to the ( $V_{REF}$ ).

Fig. 3. Operational waveform of the proposed digital LDO.

### **B.** LTTC Comparator

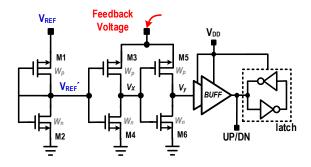

The Logic Threshold Trigger Comparator (LTTC) functions as the primary sensing mechanism, continuously comparing the output voltage ( $V_{OUT}$ ) with the reference voltage ( $V_{REF}$ ). The comparator generates a UP\_DN signal, providing directional guidance for voltage adjustments. This real-time feedback is pivotal for maintaining system stability and mitigating transient deviations as shown in Fig. 4.

Fig. 4. Schematic of the LTTC-based comparator.

Fig. 5. Schematic of the LTTC-based comparator.

### C. Voltage Range Detector

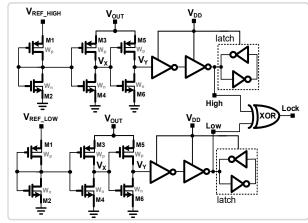

The Voltage Range Detector extends the monitoring capabilities by comparing (VOUT) against predefined thresholds voltage, (VREF\_High) and (VREF\_Low). This comparison generates three critical signals: (High), (Low), and (Lock), as shown in Fig. 5, which collectively indicate whether (VOUT) is within the desired operational range. The lock signal serves as a central control indicator, guiding the activation of appropriate control loops to enable both rapid corrective action and fine-tuned voltage adjustments.

### D. Edge Detector

The Edge Detector is responsible for identifying transitions in the High and Low signals, which indicate variations in  $V_{OUT}$  due to dynamic load conditions. It continuously monitors these signals and detects state changes, whether from high to low or low to high.

Upon recognizing such transitions, the Edge Detector generates a Trigger signal, which serves as an essential input to the Glitch signal block. By accurately capturing these transitions, the Edge Detector ensures that the system responds promptly to fluctuations in  $V_{OUT}$ , enabling precise activation of the voltage regulation mechanism.

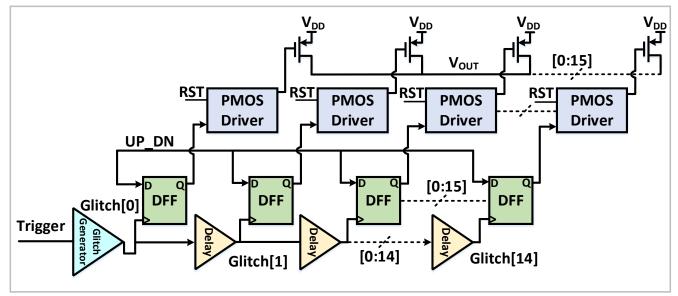

# E. Dynamic Control System for Fast and Stable Voltage Regulation

The proposed digital LDO features a dual-loop control system consisting of a Fast-Adaptive Response Controller and a Fine Voltage Stabilizer controller. These subsystems work in tandem to effectively manage dynamic voltage scaling, providing both fast transient response and precise steady-state voltage regulation. This collaboration enables the LDO to handle substantial load variations while ensuring the stability of the output voltage  $(V_{OUT})$  with high accuracy. The architecture of the Fast-Adaptive Response Controller is depicted in Fig. 7. The Fast-Adaptive Response Controller is responsible for coarse voltage adjustments during transient events where (V<sub>OUT</sub>) deviates significantly from the reference voltage range. When (V<sub>OUT</sub>) falls outside this range, a trigger is activated by the voltage range detector comparator, which identifies whether (V<sub>OUT</sub>) is too high or too low. Based on this, the edge detector turns the Fast-Adaptive Response Controller on or off, by generating a precise glitch pulse. These signals are fed into the controller's asynchronous logic, driven by a glitch generator that produces a clockless short pulse with a fixed pulse width to trigger a series of D flip-flops (DFFs) in the control path. Each D flip-flop (DFF) controls a segment of the PMOS driver circuit, enabling or disabling individual PMOS switches in the segmented array. The PMOS driver ensures that the PMOS switches remain OFF during startup, preventing unintended activation and excessive power dissipation. Once the system transitions from startup to active regulation, the PMOS driver responds to control signals from the adaptive controller, selectively activating the appropriate number of PMOS switches to regulate (V<sub>OUT</sub>) efficiently. This controlled activation mechanism prevents sudden voltage spikes and enhances the overall stability of the DLDO system. The segmented PMOS array is a critical component of the coarse control mechanism. It consists of

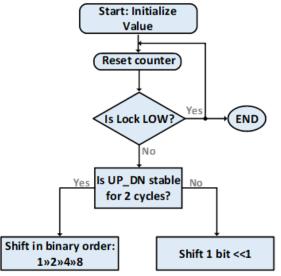

Fig. 6. Flowchart of the proposed fine stabilizer controller.

Fig. 7. Schematic diagram of the proposed fast adaptive response controller.

16 PMOS switches, each responsible for supplying a specific amount of current based on which segment is activated. During a transient event, such as a sudden increase in load current (ILOAD), the controller activates multiple PMOS switches simultaneously, allowing substantial current to flow and quickly restore (V<sub>OUT</sub>) to the desired level. Once the transient is addressed and (V<sub>OUT</sub>) stabilizes near the reference voltage range, the controller transitions to fine control, which is managed by the Fine Voltage Stabilizer to maintain precise stability. The flowchart for the Fine Voltage Stabilizer, as depicted in Fig. 6, demonstrates a structured approach for achieving precise voltage adjustments during steady-state operation. The fine stabilizer controller follows a structured sequence to regulate (V<sub>OUT</sub>) effectively. First, the controller initializes, preparing the system for voltage regulation. Following this, the reset counter is activated, clearing any previous values to ensure a fresh start for the control process. This reset step is essential for maintaining accuracy in subsequent voltage adjustments. After resetting, the system evaluates the Lock signal, which determines whether  $(V_{OUT})$  is within the acceptable range. If the Lock signal is (LOW), it signifies that no further voltage correction is needed, and the process is terminated. However, if Lock remains (HIGH), indicating a deviation from V<sub>REF</sub>, the controller proceeds to analyze the behavior of the (UP\_DN) signal over two clock cycles to decide the appropriate adjustment mode. The fine stabilizer operates in two distinct modes, depending on the stability of the (UP\_DN) signal. If (UP\_DN) remains constant for two consecutive clock cycles, it indicates that (V<sub>OUT</sub>) is significantly above or below (V<sub>REF</sub>), suggesting a large deviation that requires a rapid correction. In this case, the system applies binary order shifting, where the adjustment step size increases progressively, following the sequence (e.g.,  $1 \rightarrow 2 \rightarrow 4 \rightarrow 8$ ). This approach enables a faster response to significant voltage deviations, expediting the recovery process. On the other hand, if (UP DN) fluctuates within two clock cycles, it suggests that (V<sub>OUT</sub>) is approaching  $(V_{REF})$  and requires more precise control to

avoid excessive correction. In this scenario, the system applies a 1-bit-at-a-time shift, ensuring finer voltage regulation and preventing overshoot.

### III. RESULTS AND DISCUSSION

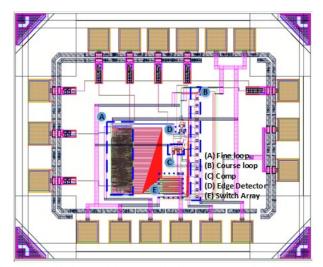

The proposed Fast Adaptive Response-based digital LDO was designed in a 65 nm CMOS process, occupying an active area of 0.098 mm<sup>2</sup>, as shown in Fig. 8. This design achieves regulated output voltage ( $V_{OUT}$ ) in the range of 0.55 V–1.15 V with a dropout voltage ( $V_{DO}$ ) as low as 50 mV, demonstrating excellent performance metrics in both steady-state and transient response. The load current ( $I_{LOAD}$ ) is regulated over a wide range from 500µA to 22mA, while maintaining a compact design and competitive performance across key parameters, including recovery time, voltage ripple, and line regulation.

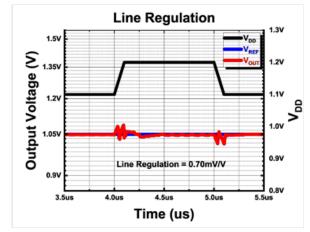

The line regulation performance of the proposed Fast Adaptive Response-based digital LDO is depicted in Fig. 9. The simulation evaluates the ability of the output voltage  $(V_{OUT})$  to maintain stability in response to variations in the

Fig. 8. Chip layout of the proposed adaptive response digital LDO.

supply voltage ( $V_{DD}$ ) while the reference voltage ( $V_{REF}$ ) is held constant at 1.05 V. During the test, ( $V_{DD}$ ) is varied from 1.1 V to 1.2 V and then back to 1.1 V. The results show that ( $V_{OUT}$ ) remains closely aligned with ( $V_{REF}$ ), with only minimal deviations observed during the transition.

The calculated line regulation is approximately 0.70 mV/V, indicating a strong ability of the proposed design to suppress supply voltage disturbances. This performance is achieved through the integration of the fast-adaptive response controller and fine voltage stabilizer, which dynamically adjust the PMOS switches to counteract any variations in ( $V_{DD}$ ). The smooth response of ( $V_{OUT}$ ) with negligible ripple further demonstrates the robustness of the proposed architecture.

Fig. 9. Simulated line regulation of the proposed digital LDO.

This superior line regulation highlights the capability of the proposed digital LDO to provide consistent output voltage across a wide range of supply voltage variations. Such performance is essential for power management systems in SoCs, ensuring reliable operation even under fluctuating power supply conditions.

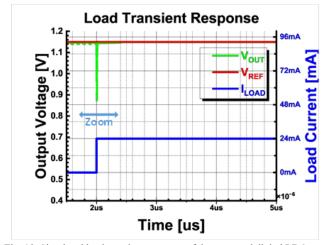

The load transient response of the proposed Fast Adaptive Response-based digital LDO is demonstrated in Fig. 10. This simulation evaluates the output voltage ( $V_{OUT}$ ) behavior under a step load current ( $I_{LOAD}$ ) transition from 0 mA to 24 mA. At the onset of the load step, ( $V_{OUT}$ ) experiences a

Fig. 10. Simulated load transient response of the proposed digital LDO.

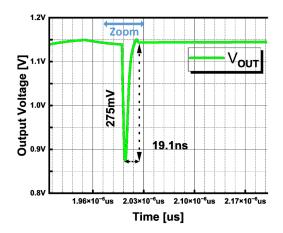

temporary undershoot of 275 mV due to the rapid increase in ( $I_{LOAD}$ ). However, the proposed architecture ensures a fast recovery, with ( $V_{OUT}$ ) stabilizing to the reference voltage ( $V_{REF}$ ) within a transient recovery time of 19.1 ns. This rapid recovery is attributed to the Fast-Adaptive Controller, which dynamically adjusts the PMOS switches to counteract the voltage dip effectively. In the broader context depicted in Fig. 11, ( $V_{OUT}$ ) remains stable and closely tracks ( $V_{REF}$ ) after the transient state, maintaining output regulation despite the significant load current variation. The steady-state performance demonstrates the robustness of the proposed

Fig. 11. Simulated zoom part of the load transient response.

design in mitigating ripple and ensuring minimal deviation from ( $V_{REF}$ ).

These results underscore the superior transient response capability of the proposed LDO, achieving both minimal undershoot and fast recovery, which are critical for modern power management ICs in dynamic operating environments.

The performance of the proposed fast-adaptive responsebased digital LDO is compared with recent state-of-the-art digital LDOs as shown in Table I, unlike conventional designs, the proposed LDO demonstrates substantial improvements in key performance metrics while maintaining a minimal output capacitance of 0.1 nF.

The evaluation is based on two critical figures of merit (FOM<sub>1</sub> and FOM<sub>2</sub>), highlighting the superiority of the proposed approach. The proposed design achieves a transient recovery time (T<sub>REC</sub>) of 19.11 ns for a voltage undershoot of 264 mV during a load current step of 22.4 mA, significantly outperforming the designs in [15], [16], and [17]. Additionally, the  $FOM_2$  of the proposed design is remarkably low at 0.225 ns<sup>2</sup>, which is substantially better than the values reported in [15], [16], [17] and [18]. This demonstrates the efficiency of the adaptive search controller in delivering faster recovery times with minimized energy costs. Despite its compact size, with an active area of just 0.098 mm<sup>2</sup>, the proposed LDO achieves high performance across all metrics, making it a suitable choice for modern system-on-chip (SoC) applications. The comparative analysis underscores the balance achieved by the proposed design in minimizing recovery time, reducing undershooting, and maintaining high efficiency, establishing it as a leading solution among state-of-the-art digital LDOs. remarkably

|                                         | This Work         | [15]            | [16]              | [17]      | [18]      |

|-----------------------------------------|-------------------|-----------------|-------------------|-----------|-----------|

| Process [nm]                            | 65                | 3 GAAFET        | 65                | 65        | 65        |

| Topology                                | Adaptive +<br>SRs | TEC Distributed | Adaptive Sampling | PID       | AS+CEA    |

| V <sub>DD</sub> [V]                     | 0.6-1.2           | 0.55-1.1        | 0.6-1.2           | 0.7-1.3   | 0.6-1.2   |

| V <sub>OUT</sub> [V]                    | 0.55-1.15         | 0.5-1.05        | 0.5-1.1           | 0.65-1.25 | 0.55-1.15 |

| I <sub>LOAD, MAX</sub> [mA]             | 23                | 10000           | 62                | 80        | 26        |

| C <sub>OUT</sub> [nF]                   | 0.1               | 320             | 0.1               | 0.0095    | 0.01      |

| $V_{OUT}[mV]@$<br>$\Delta I_{LOAD}[mA]$ | 264@22.4          | 94@6500         | 145@31.6          | 275@28    | 140@26    |

| $T_{REC}[ns]@$<br>$\Delta V_{OUT}[mV]$  | 19.11@264         | 200*@94         | 600*@145          | 60*@275   | 95@140    |

| $\Delta I_{LOAD}T_{EDGE}[ns]$           | 1                 | 1               | 48                | 0.1       | 20        |

| I <sub>Q</sub> [uA]                     | 157               | 18170           | 17.4              | 1050      | 167       |

| Current Eff. [%]                        | 99.32             | 99.82           | 99.99             | 99.75     | 99.6      |

| FOM <sub>1</sub> [ps]                   | 11.8              | 14.3            | 13.5              | 5.37      | 39.4      |

| FOM <sub>2</sub> [ns <sup>2</sup> ]     | 0.225             | 2.87            | 8.08              | 0.322     | 3.74      |

| Active Area [mm <sup>2</sup> ]          | 0.098             | 0.038           | 0.0670            | 0.0925    | 0.075     |

TABLE I. Performance Comparison of the Proposed Fast-Adaptive Response-Based Digital LDO with State-of-the-Art Designs.

\* Estimated from measurement

$$FOM_{1} = \frac{C_{LOAD} \times \Delta V_{OUT} \times I_{Q}}{\Delta I_{LOAD}^{2}} + \frac{T_{EDGE} \times I_{Q}}{2\Delta I_{LOAD}}$$

$FOM_2 = FOM_1 \times T_{REC}$

low at 0.225 ns<sup>2</sup>, which is substantially better than the values reported in [15], [16], [17] and [18]. This demonstrates the efficiency of the adaptive search controller in delivering faster recovery times with minimized energy costs. Despite its compact size, with an active area of just 0.098 mm<sup>2</sup>, the proposed LDO achieves high performance across all metrics, making it a suitable choice for modern system-on-chip (SoC) applications. The comparative analysis underscores the balance achieved by the proposed design in minimizing recovery time, reducing undershooting, and maintaining high efficiency, establishing it as a leading solution among state-of-the-art digital LDOs.

### IV. CONCLUSION

Efficient power management in System-on-Chip (SoC) platforms faces increasing challenges due to aggressive device scaling and dynamic load conditions. This study presents a fast-adaptive digital Low-Dropout Regulator (DLDO) architecture that addresses these challenges with a clockless Logic Threshold Triggered Comparator (LTTC) for asynchronous feedback. The dual-loop control strategy combines a coarse loop for rapid voltage correction during transients and a fine stabilizer for precise steady-state regulation, significantly improving transient recovery time (T<sub>REC</sub>) and minimizing output ripple while maintaining low quiescent current (I<sub>0</sub>). By eliminating clock dependencies and incorporating a glitch-driven control mechanism, the proposed DLDO demonstrates robust, energy-efficient performance across dynamic load conditions, making it highly suitable for next-generation SoC applications.

### ACKNOWLEDGMENT

The chip fabrication and EDA tool were supported by the IC Design Education Center (IDEC), Korea.

#### REFERENCES

- Huang, Mo, Yan Lu, and Rui P. Martins. "A comparative study of digital low dropout regulators." Journal of Semiconductors 41.11 (2020): 111405.

- [2] Lai, Li Fang, et al. "Design Trends and Perspectives of Digital Low Dropout Voltage Regulators for Low Voltage Mobile Applications: A Review." IEEE Access (2023).

- [3] Akram, M., Hwang, I., & Ha, S. (2020). Architectural Advancement of Digital Low-Dropout Regulators. IEEE Access, 8, 137838-137855.

- [4] Chen, Y., & Chen, C. (2023). An Event-Driven Self-Clocked Digital Low-Dropout Regulator with Adaptive Frequency Control. Energies.

- [5] Cai, G., Zhan, C., & Lu, Y. (2019). A Fast-Transient-Response Fully-Integrated Digital LDO With Adaptive Current Step Size Control. IEEE Transactions on Circuits and Systems I: Regular Papers, 66, 3610-3619.

- [6] Park, J., Hwang, J., Oh, J., & Jeong, D. (2020). 32.4 A 0.4-to-1.2V 0.0057mm2 55fs-Transient-FoM Ring-Amplifier-Based Low-Dropout Regulator with Replica-Based PSR Enhancement. 2020 IEEE International Solid- State Circuits Conference - (ISSCC), 492-494.

- [7] Jayaraman, K., Rawy, K., & Kim, T. (2016). A 0.6-V power efficient digital LDO with 99.7% current efficiency utilizing load current aware clock modulation for fast transient response. 2016 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), 103-106.

- [8] Akram, M., Hong, W., & Hwang, I. (2018). Fast Transient Fully Standard-Cell-Based All Digital Low-Dropout Regulator With 99.97% Current Efficiency. IEEE Transactions on Power Electronics, 33, 8011-8019.

- [9] Kang, J., Park, J., Jeong, M., & Yoo, C. (2022). Digital Low-Dropout Regulator With Voltage-Controlled Oscillator Based Control. IEEE Transactions on Power Electronics, 37, 6951-6961.

- [10] Cai, G., Zhan, C., & Lu, Y. (2019). A Fast-Transient-Response Fully-Integrated Digital LDO with Adaptive Current Step Size Control. 2019 IEEE International Symposium on Circuits and Systems (ISCAS), 1-4.

- [11] M. A. Akram, W. Hong, S. Ha and I. -C. Hwang, "Capacitor-Less Dual-Mode All-Digital LDO With ΔΣ-Modulation-Based Ripple Reduction," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 68, no. 5, pp. 1620-1624, May 2021

- [12] Shi, J., Zhao, B., Tang, Z., P., & Di, Z. (2020). A selfclocked binary-seaching digital low-dropout regulator with fast transient response. IEICE Electron. Express, 17, 20200297.

- [13] Lim, C., Mandal, D., Bakkaloglu, B., & Kiaei, S. (2017). A 50-mA 99.2% Peak Current Efficiency, 250-ns Settling Time Digital Low-Dropout Regulator With Transient Enhanced PI Controller. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 25, 2360-2370.

- [14] Hwang, Y., Oh, J., Choi, W., Jeong, D., & Park, J. U (2022). A Residue-Current-Locked Hybrid Low-Dropout Regulator Supporting Ultralow Dropout of Sub-50 mV With Fast Settling Time Below 10 ns. IEEE Journal of Solid-State Circuits, 57, 2236-2249.

- [15] D. Lee, "A 10A computational digital LDO achieving 263A/mm2 current density with distributed powergating switches and time-based fast-transient controller for mobile SoC application in 3nm GAAFET," in IEEE Int. Solid-State Circuits Conf.(ISSCC) Dig. Tech. Papers, 2024, pp. 264-266.

- [16] S. Yamaguchi, T. Hisakado, O. Wada, and M. Islam, "A Fully Integrated Digital LDO With Adaptive Sampling and Statistical Comparator Selection," IEEE Solid-State Circuits Letters, 2024.

- [17] Y. K. Cherivirala and D. D. Wentzloff, "A capacitorless digital LDO regulator with synthesizable PID controller achieving 99.75% efficiency and 93.3-ps response time in 65 nm," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 70, no. 5, pp. 1769-1773, 2023.

- [18] J.-W. Jang, I. A. Wahla, J. Choi, M. A. Akram, and I.-C. Hwang, "A Fast-Transient Fully-Integrated Digital LDO with Current-Estimation Algorithm based Coarse Loop," IEEE Transactions on Power Electronics, 2023.

**IBRAR ALI WAHLA** received the B.E. degree in Electronics Engineering from the Pakistan Air-Force Karachi Institute of Technology Engineering and (PAF-KIET), Karachi, Pakistan, in 2016, and the M.S. degree in Electronics Engineering from Hallym University, Chuncheon, South Korea, in 2021. He is currently pursuing a Ph.D. in

Electrical and Medical Convergent Engineering at Kangwon National University, South Korea, beginning in 2021.

His research interests include analog and mixed-signal CMOS integrated circuits, embedded systems, digital integrated circuit design, and power management. His work has primarily focused on developing advanced solutions for efficient energy utilization and miniaturization of circuitry in Power management.

### MUHAMMAD ABRAR AKRAM

(Member, IEEE) received the B.S. degree in Electrical Engineering from the University of Punjab, Lahore, Pakistan, in 2013, and a combined M.S. and Ph.D. degree in Electrical and Medical Convergent Engineering from the Kangwon National University, Chuncheon, South Korea, in 2019.

From 2019 to 2023, he was a Post-Doctoral Associate with the Engineering Division, New York University Abu Dhabi, Abu Dhabi, UAE, where he extensively worked on the sensing-interface circuits. After a rewarding Post-Doctoral tenure, Dr. Akram joined the Department of Electrical Engineering, Qatar University, Doha, Qatar in 2024, as an

Assistant Professor. His research interests include analog/mixed-signal CMOS integrated circuits for power management in system-on-chip devices, wireless-powered mm-scaled biomedical implants, and sensing interface circuits.

### IN-CHUL HWANG (S'93-M'95-

SM'18) received the B.S., M.S., and Ph.D. degrees from Korea University, Seoul, South Korea, in 1993, 1995, and 2000, respectively. He was a Post-Doctoral Associate with the Coordinated Science

Laboratory, University of Illinois at Urbana–Champaign, Urbana, IL, USA, from 2000 to 2001. In 2001, he joined Samsung Electronics, System LSI Division, Kiheung, South Korea, where he led a design team for developing CMOS

Global System for Mobile Communication (GSM)/ Enhanced Data for GSM Evolution/Wideband Code Division Multiple Access RF transceiver.

Since 2007, he has been with the Department of Electrical and Electronics Engineering, Kangwon National University, Chuncheon, South Korea, where he is currently a professor. He was a Visiting Scholar with the Georgia Institute of Technology, Atlanta, GA, USA, in 2012. His current research interests include digital phase-locked loops for radio-frequency integrated circuits and power management circuits for dynamic-voltage and frequency scaling applications.

Dr. Hwang was a recipient of the LG Design Contest Grand Prize in 1999 and the DAC Student Design Contest Award in 2002.