# An Adaptive Gate Driver-Assisted Continuously Scalable-Conversion-Ratio Switched-Capacitor Converter

## Seokhee Han<sup>1</sup> and Chulwoo Kim<sup>a</sup>

Department of Electrical Electronic Engineering, Korea University E-mail: ¹hsh@kilby.korea.ac.kr

Abstract - This paper presents an adaptive gate driver-assisted continuously scalable-conversion-ratio (CSCR) switched-capacitor (SC) DC-DC converter. Gate-source voltage controller (GSVC) generates dynamic supply voltage to the gate driver adaptively according to the output voltage level of the converter. By adopting an adaptive gate driver to achieve soft charging between capacitor connections, the overall system generates a wide range of output with high power density and power conversion efficiency. The proposed converter generates an output range from 0.7 V to 1.8 V from an input voltage of 2.9 V. The proposed converter achieves a peak PCE of 72%. The proposed converter is implemented in TSMC 180 nm BCD process, with a chip area of 3 mm x4 mm.

Keywords— Switched-capacitor converter, PMIC, voltage-conversion-ratio

#### I. INTRODUCTION

In recent years, Internet of Things (IoT) technologies have been advanced to perform multiple operations with limited hardware resources. To support the end nodes of IoT applications to achieve high performance, various multicore-based system-on-chip (SoC) designs have been introduced recently. However, to improve the battery lifetime of IoT nodes, the power management integrated circuit (PMIC) should provide a per-core dynamic voltage and frequency scaling (DVFS) scheme [1] to improve the energy efficiency of digital loads.

Switched capacitor (SC) DC-DC converters have been widely studied due to their compatibility with on-chip applications. Although these SC converters require more complex hardware designs to provide a wide output voltage  $(V_{\rm OUT})$  range, the converters achieve higher power density than inductor-based converters and higher PCE than LDO regulators [2]-[3]. Therefore, a wide  $V_{\rm OUT}$  switched capacitor (SC) converter is a key component in the implementation of battery-powered IoT nodes for small form factors and long battery lifetime.

#### a. Corresponding author; ckim@korea.ac.kr

Manuscript Received Dec. 19, 2024, Revised Feb. 12, 2025, Accepted Feb. 12, 2025

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<a href="http://creativecommons.org/licenses/by-nc/4.0">http://creativecommons.org/licenses/by-nc/4.0</a>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

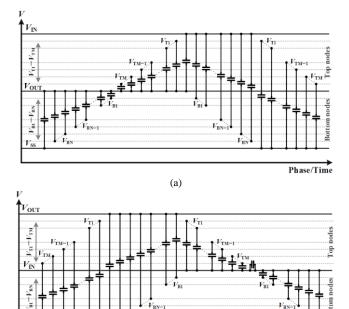

Fig. 1. Voltage versus phase diagram topology of (a) conventional single-output step-down CSCR SC converter [4] and (b) conventional single-output step-up CSCR SC converter [5].

#### II. EXPERIMENTS

### A. Prior Works

Recently, continuously scalable-conversion-ratio (CSCR) SC topologies have been proposed to overcome the discontinuity of VCR [4]-[9]. Compared with other hybrid buck-boost converters, these converters perform soft charging between flying capacitors ( $C_{\rm core}$ s) by changing the hardware connections between  $C_{\rm core}$ s in each phase. Therefore, the CSCR SC converters have multiple SC cores that perform interleaved charge-sharing operations. Fig. 1 shows the hardware connections of the single  $C_{\rm core}$  of conventional CSCR SC converters. In the design of CSCR SC converters, the hardware connection sequences between the  $C_{\rm core}$ s determine the power conversion operation of the CSCR SC converter [4]. For example, the SC core in Fig. 1(a) performs step-down conversion and the SC core in Fig. 1(b) performs step-up conversion. These CSCR SC

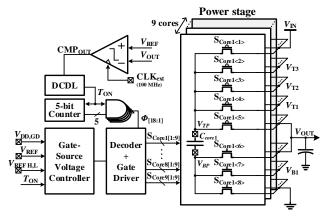

Fig. 2. Top block diagram of the proposed adaptive gate driver assisted CSCR SC converter.

converters perform power conversion operations with low charge-sharing losses and bottom plate losses. However, increasing the number of SC core cells results in larger hardware areas for the controller and gate drivers, as well as increased hardware complexity. And reducing the number of SC core cells results in an increase in charge-sharing losses due to hard-charging between the  $C_{\rm core}$ s.

#### B. Top Architecture

Fig. 2 shows the top block diagram of the proposed adaptive gate driver-assisted CSCR SC converter. The proposed converter adopts a CSCR SC power stage consisting of the number of nine SC core cells, and each SC core cell consists of five switches at the top node of  $C_{\text{core}}$ (three switches connected to the top flying nodes ( $V_{T1-3}$ ) and switches for  $V_{\rm OUT}$  and  $V_{\rm IN}$ ) and three switches at the bottom node of  $C_{core}$  (one switch connected to the bottom flying node  $(V_{\rm B1})$  and switches for  $V_{\rm OUT}$  and  $V_{\rm SS}$ ). The output of a dynamic comparator (CMP<sub>OUT</sub>) triggers the on-time signal  $(T_{\rm ON})$  by comparing  $V_{\rm OUT}$  with its reference voltage  $(V_{\rm REF})$ .  $V_{\text{OUT}}$  is regulated by controlling the off-time between each  $T_{\rm ON}$  pulse, the pulse width of which is determined by the digital controller delay line (DCDL). The five AND gates sequentially distribute the  $T_{\rm ON}$  signal into 18 phase signals  $(\Phi_{[1:18]})$ , which generate signals to drive the power stage through the decoder. The gate-source voltage controller (GSVC) adaptively supplies the gate drivers with voltage  $(V_{\rm DD}, \, {\rm GND})$  by monitoring  $V_{\rm REF}$  and comparing it with reference voltages ( $V_{REF,H}$  and  $V_{REF,L}$ ).

### C. GSVC Circuit

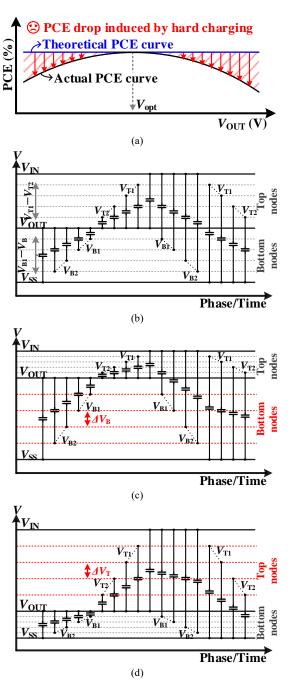

Fig. 3(a) shows the design target of the GSVC circuit. The CSCR SC topology exhibits a flat power conversion efficiency (PCE) curve, which is achieved by suppressing hard charging through gradual charge sharing between  $C_{\rm core}$ s. However, the deviation of the output voltage from the optimum voltage ( $V_{\rm opt}$ ) at which the flying nodes ( $V_{\rm T1-2}$ ,  $V_{\rm B1-2}$ ) are uniformly distributed (as shown in Fig. 3(b)) causes the loss of charge sharing through hard charging operation, resulting in a decrease in PCE in the practical implementation of the CSCR SC topology. The case where

Fig. 3. Design target of GSVC for the wide output voltage range (a), the voltage versus phase diagram topology of optimum output voltage (b), the upper voltage level of  $V_{\rm opt}$  (c), and the lower voltage level of  $V_{\rm opt}$  (d).

$V_{\rm OUT}$  is regulated at the upper level of  $V_{\rm opt}$ , the voltage difference of the bottom flying nodes ( $\Delta V_{\rm B}$ ) is increased as shown in Fig. 3(c), resulting in charge-sharing loss at the bottom node connection between  $C_{\rm core}$ s. Regulating  $V_{\rm OUT}$  at the lower level of  $V_{\rm opt}$  increases the voltage difference ( $\Delta V_{\rm T}$ ) between the top flying nodes as shown in Fig. 3(d), resulting in charge-sharing loss at the top node connection.

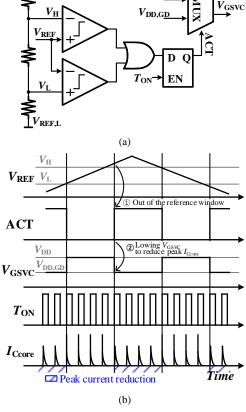

Fig. 4 shows the circuit implementation of the GSVC. The GSVC employs two static comparators to compare  $V_{\rm REF}$  and  $V_{\rm REF,H,L}$ , which are divided by resistors into  $V_{\rm H}$  and  $V_{\rm L}$  signals, respectively. When the  $V_{\rm REF}$  deviates from the voltage range of  $V_{\rm H}$  and  $V_{\rm L}$ , the activate signal (ACT) is generated. The

$V_{

m REF,H}$

Fig. 4. (a) Circuit implementation of the gate-source voltage controller and (b) operation of the proposed converter.

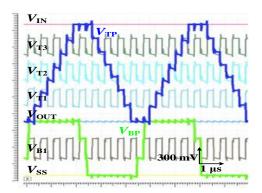

Fig. 5. Simulated waveforms of the internal nodes of the converter.

ACT signal transits through a latch when  $T_{\rm ON}$  is high, preventing abnormal switching operation. Based on the ACT signal, the supply voltage of the switch drivers is set to either  $V_{\rm DD}$  or  $V_{\rm DD,GD}$ . The gate driver voltage level reduces the peak hard-charging current between  $C_{\rm core}$ s ( $I_{\rm Ccore}$ ) by lowering the gate-source voltage of the switch, which increases its onresistance.

Fig. 5 shows the simulation results of the internal voltage waveforms of the proposed converter. The three top flying nodes and one bottom flying node toggle voltages evenly, facilitated by charge sharing across the nine cores. Consequently, the  $C_{\rm core}$ s of the CSCR cores swing as follows: the top plate nodes swing from  $V_{\rm OUT}$  to  $V_{\rm IN}$  through the flying nodes, while the bottom flying nodes swing from  $V_{\rm SS}$  to  $V_{\rm OUT}$ . As a result, the flying nodes stepwise swing from  $V_{\rm SS}$  to  $V_{\rm IN}$  via the flying nodes.

Fig. 6. Simulated  $I_{OUT}$  load transient waveforms.

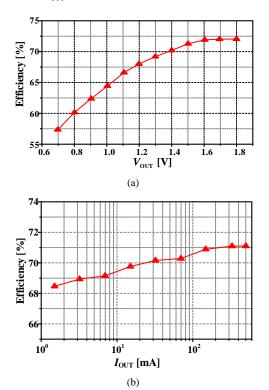

Fig. 7. Simulated power conversion efficiency plots (a) with respect to  $V_{\rm OUT}$  at  $V_{\rm IN}=2.9~{\rm V}$  and  $R_{\rm OUT}=5\Omega$ , and (b) with respect to  $I_{\rm OUT}$  at  $V_{\rm IN}=2.9~{\rm V}$  and  $V_{\rm OUT}=1.5~{\rm V}$ .

## III. RESULTS AND DISCUSSION

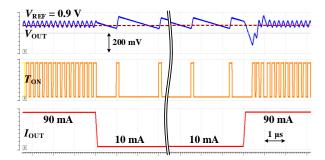

Fig. 6 shows simulated load transient waveforms of the converter. During the load transient from 10 mA to 90 mA, the output voltage is regulated by off-time modulation, tracking the reference voltage. Fig. 7 shows the simulated PCE results of the proposed converter. The converter covers an output voltage range of 0.7 V to 1.8 V from  $V_{\rm IN}$  of 2.9 V as shown in Fig. 7(a). Additionally, the converter supplies  $I_{\rm OUT}$  ranging from 1.5 mA to 500 mA at  $V_{\rm OUT}$  of 1.5 V and  $V_{\rm IN}$  of 2.9 V as shown in Fig. 7(b).

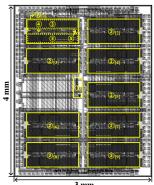

Fig. 8 shows the chip layout of the proposed converter. The converter is fabricated using a 180 nm BCD process, with a chip area of 3 mm x 4 mm. For the high load current, the size of the power switches was designed large. It is designed that the power switches are placed along the pad lines to reduce the length of the power metal lines and improve the PCE. The control circuits are placed at the center of the chip so that the control signals for the power stages travel through the short route.

- ① Controller ②[i] i<sup>th</sup> CSCR cell

- (3) 1st CSCR cell switches (4) 1st CSCR cell gate drivers

- ⑤ 1<sup>st</sup> CSCR cell decoder

Fig. 8. Chip layout.

TABLE I. Comparison with state-of-the-art SC converters.

|                               | [2]               | [3]                 | [4]                 | [8]                | This Work         |

|-------------------------------|-------------------|---------------------|---------------------|--------------------|-------------------|

| Process                       | 65nm CMOS         | 180nm BCD           | 28nm CMOS           | 65nm CMOS          | 180nm BCD         |

| $V_{\mathrm{IN}}(\mathrm{V})$ | 1.5               | 2.5-5               | 2                   | 0.4-2.5            | 2.9-3             |

| V <sub>OUT</sub> (V)          | 0.18-1.19         | 0.1-3.67            | 0-2.22              | 0.4-2              | 0.7-1.8           |

| # of VCR                      | 4                 | 9                   | CSCR                | CSCR               | CSCR              |

| C <sub>FLY,total</sub> (nF)   | 400<br>(Off-chip) | 49.23<br>(MOS, MIM) | 0.458<br>(MOS, MOM) | 19.8<br>(MOS, MOM) | 300<br>(Off-chip) |

| I <sub>OUT,max</sub> (mA)     | 400               | 362*                | 3*                  | 19.8*              | 500               |

| PCE <sub>max</sub> [%]        | 93.7              | 87                  | 93                  | 90                 | 72                |

<sup>\*</sup> Estimated based on the study

#### IV. CONCLUSION

Table I presents a performance comparison of the conventional step-down SC converters with a wide  $V_{\rm OUT}$  range. This paper illustrated the adaptive gate driver-assisted CSCR SC converter. The power stage is composed of nine CSCR core cells with three top-flying nodes and one bottom-flying node. The proposed GSVC reduces the capacitor current modulating  $V_{\rm GS}$  of power switches, so the energy loss mechanism between the  $C_{\rm core}$  connections is changed from hard charging to soft charging-based operation. As a result, the converter achieves a wide output voltage range beyond the non-optimal VCR range.

#### ACKNOWLEDGMENT

The chip fabrication and Electronic Design Automation (EDA) tools were supported by the IC Design Education Center (IDEC), Daejeon, South Korea.

#### REFERENCES

- [1] K. Wonyoung, M. S. Gupta, W. Gu-Yeon, and D. Brooks, "System level analysis of fast, per-core DVFS using on-chip switching regulators," in *Proc. High Perform. Comput. Archit.*, Feb. 2008, pp. 123–134.

- [2] Y. Jiang et al., "Arithmetic Progression Switched-Capacitor DC–DC Converter Topology With Soft VCR Transitions and Quasi-Symmetric Two-Phase Charge Delivery," *IEEE* J.Solid-State Circuits, vol. 57, no. 10, pp. 2919-2933, Oct. 2022

- [3] H. Kim et al., "A Fully Integrated Nine-Ratio Switched-Capacitor Converter With Overlapped-Conversion-Ratio Modulation for IoT Applications," *IEEE J. Solid-State Circuits*, vol. 59, no. 10, pp. 3444-3456, Oct. 2024

- [4] N. Butzen and M. Steyaert, "Design of single-topology continuously scalable-conversion-ratio switched-capacitor DC–DC converters," *IEEE* J. Solid-State Circuits, vol. 54, no. 4, pp. 1039–1047, Apr. 2019...

- [5] H. Kim, J. Maeng, I. Park, J. Jeon, Y. Choi, and C. Kim, "A dual-mode continuously scalable-conversion-ratio SC energy harvesting interface with SC-based PFM MPPT and flying capacitor sharing scheme," *IEEE* J.Solid-State Circuits, vol. 56, no. 9, pp. 2724–2735, Sep. 2021. 4

- [6]H. Gi, J. Park, Y. Yoon, S. Jung, S. J. Kim, and Y. Lee, "A soft-charging-based SC DC–DC boost converter with conversion-ratio-insensitive high efficiency for energy harvesting in miniature sensor systems," *IEEE* Trans. Circuits Syst. I, Reg. Papers, vol. 67, no. 10, pp. 3601–3612, Oct. 2020.

- [7] Y. Yoon et al., "A continuously-scalable-conversion-ratio step-up/down SC energy-harvesting interface with MPPT enabled by real-time power monitoring with frequency-mapped capacitor DAC," *IEEE* Trans. Circuits Syst. I, Reg. Papers, vol. 69, no. 4, pp. 1820–1831, Apr. 2022.

- [8] Y. Wang, M. Hwang, Y. Lu, R.Martins, , "A Continuously Scalable-Conversion-Ratio SC Converter with Reconfigurable VCF Step for High Efficiency over an Extended VCR Range," 2023 IEEE International Solid-State Circuits Conference (ISSCC), 2023, pp. 450-451.

- [9] N. Butzen, et al., "A Monolithic 26A/mm2 Imax, 88.5% Peak- Efficiency Continuously Scalable Conversion-Ratio Switched-Capacitor DC-DC Converter," 2023 *IEEE* International Solid-State Circuits Conference (*ISSCC*), 2023, pp. 232-233.

converters.

**Seokhee Han** (Graduate Student Member, *IEEE*) received the B.S. in electrical engineering at Korea University, Seoul, South Korea, in 2023, where he is currently pursuing the M.S. degree.

His research interests integrated power management system designs and low-power CMOS analog circuit designs, and DC-DC power

Chulwoo Kim (Senior Member, *IEEE*) received the B.S. and M.S. degrees in electronics engineering from Korea University in 1994 and 1996, respectively, and the Ph.D. degree in electrical and computer engineering from the University of Illinois at Urbana-Champaign in 2001.

In May 2001, he joined IBM Microelectronics Division, Austin, TX, where he was involved in Cell processor design. Since September 2002, he has been with the School of Electrical Engineering, Korea University, where he is currently a Professor. He was a Visiting Professor at the University of California at Los Angeles in 2008 and at the University of California at Santa Cruz in 2012. He is a coauthor of two books, namely, CMOS Digital Integrated Circuits: Analysis and Design (McGraw Hill, 4th edition 2014) and High-Bandwidth Memory Interface (Springer, 2013). His current research interests are in the areas of wireline transceiver, power management, data converters, and quantum-inspired computing.

Dr. Kim received the Samsung HumanTech Thesis Contest Bronze Award (1996), the ISLPED Low-Power Design Contest Award (2001, 2014), the DAC Student Design Contest Award (2002), SRC Inventor Recognition Awards (2002), the Young Scientist Award from the Ministry of Science and Technology of Korea (2003), the Seoktop Award for excellence in teaching (2006, 2011, 2018, 2023) and ASP-DAC Best Design Award (2008) and Special Feature Award (2014), Korea Semiconductor Design Contest: Prime Minister's Award (2016). He served on the Technical Program Committee of the IEEE International Solid-State Circuits Conference and as a Guest Editor for the IEEE Journal of Solid-State Circuits. He also served as the Chair of the SSCS Seoul Chapter and as the Distinguished Lecturer of the IEEE Solid-State Circuits Society for 2015-2016. He is currently on the editorial boards of the IEEE Journal of Solid-State Circuits and Transactions on VLSI Systems and an elected AdCom member of the IEEE Solid-State Circuits Society.