# Low-Noise EEG Sensor and Neural Stimulator: For Motion and Stimulation Artifact Removal

Geunchang Seong<sup>1</sup>, Dongyeol Seok<sup>2</sup>, Minjae Kim<sup>3</sup> and Chul Kim<sup>a</sup>

Department of Bio and Brain Engineering, Korea Advanced Institute of Science and Technology E-mail: ¹sks96007@kaist.ac.kr, ²sukd10@kaist.ac.kr, ³kscimjbravo@kaist.ac.kr

Abstract – This work aims to develop a neural interface system that enables electroencephalogram (EEG) measurement in wearable equipment and eliminates stimulation artifacts by processing in miniaturized neural stimulation modules. The ASIC implements a 4-channel analog-front-end (AFE) with a high input-Z buffer, 2<sup>nd</sup> order oversampling delta-sigma ADC, stimulation noise cancellation digital processors, and digitally controlled neural stimulators into the chip. The simplified stimulation artifact rejection algorithm implemented on the digital block allows users to acquire pure neural signals while stimulating. The 3 mm x 1 mm IC chips were fabricated through the TSMC 65 nm LP process.

Keywords – biopotential recording, neural recording, stimulation artifact, motion artifact, electroencephalography

#### I. INTRODUCTION

Acquiring neural signals in a daily-life environment is an important research topic for biomedical engineers due to its usefulness. The daily-life electroencephalography (EEG) can fulfill the clinical needs for non-invasive monitoring of chronic diseases such as epilepsy [1], neurodegenerative disease, and depression disorders, and needs for other applications such as brain-machine interfaces and neuroscience research. For this reason, it has been researched to modify pre-existing clinical EEG systems to reduce the cumbersomeness of bio-potential recordings: development of dry or non-contact active electrodes to apply a more convenient user interface, miniaturized sizes, and extremely low noise for recording small amplitude biopotential.

Recently, the improvements in neural signal processing technique based on deep neural network and adaptive algorithm enables the quick and accurate classification/interpretation of neural signals, and it provides the vision of the future applicability related to the daily-life EEG

a. Corresponding author; kimchul@kaist.ac.kr

Manuscript Received Sep. 23, 2024, Revised Nov. 11, 2024, Accepted Dec. 30, 2024

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<a href="http://creativecommons.org/licenses/by-nc/4.0">http://creativecommons.org/licenses/by-nc/4.0</a>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

acquisition system. In addition, as research about the neural stimulator proceeds, the idea of a closed-loop neural interface by integrating the acquisition system, signal processor, and neural stimulator becomes a clear goal [2][3][4].

Designing an integrated system of daily-life EEG recorders and stimulators is a still challenging project, and many of the difficulties come from the artifact issues. The unstable electrode-tissue interface, especially in dry and non-contact cases, generates large motion artifacts that saturate the neural recorder and distort the signal. Moreover, in the integrated system, the stimulation artifacts also become a big issue. A large input perturbation is given to the neural recorder when the stimulator generates the output. The stimulation artifact causes a similar problem of saturating the neural recorder and missing the neural signals.

For decades, strategies for removing motion/stimulation artifacts have been researched and reported [5]. These artifacts cannot be easily removed by frequency filters, as the frequency spectra of users' everyday physical activities and the electrophysiological signals of the human body overlap. Modifying electrodes could provide a more stabilized electrode-tissue interface, and ASICs for recording EEG were introduced by boosting the input impedance and monitoring the interface changes to compensate for the artifact components [6]. Decomposition methods and algorithms (wavelet, ICA, PCA, etc.) to detect and remove motion/stimulation artifacts were reported as well. However, the post-recording process with heavy computational costs becomes an obstacle when applying the system in real-time environments.

This work aims to design a recorder and a neural stimulator that can satisfy the requirements for daily-life use. To record 4-channel EEG through the dry-contact interface, a high input impedance buffer and a low-noise oversampling delta-sigma ADC are integrated into one recorder channel [7]. An analog buffer at each channel is reset to the reference voltage in a short time (~1ms, short time considering the bandwidth of EEG) when the recorder generates saturated output so that it can prevent the loss of signal information and record the desired signal. Moreover, since the magnitude of the EEG motion artifact depends on the voltage across the input of the

recording analog front-end and the skin contact, the reset reference voltage of the buffer can be controlled and adjusted by the magnitude of the motion artifact. [8]

On-chip digital block with a stimulation artifact removal algorithm is implemented to realize real-time signal processing. The IIR adaptive filter scheme and the simplified algorithm reduced the area and power consumption of the digital block [9] and allowed users to acquire pure neural signals while stimulating at a low cost. In bio-application charge mismatch during stimulation could induce tissue damage and corrosion of stimulation electrodes. The H-bridge structure is used to realize a charge-balanced biphasic stimulator.

#### II. DESIGN METHODOLOGY

#### A. EEG Recording AFE and ADC-Direct Neural Recording

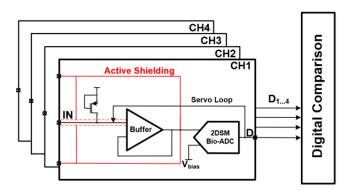

The diagram of the EEG measurement module is shown in Fig. 1. Due to the high input impedance of the analog-frontend (AFE) buffer, EEG can be recorded without large signal attenuation. Also, by shielding the input node with the output of the buffer (i.e., active shielding), power line interference such as 50/60Hz noise is significantly reduced. Input is biased with a certain DC voltage level, and a digital DC servo loop is designed to prevent saturation of output and stabilize the overall system for using ADC output. The overall chip has 4-channel recording, which can improve the post-processing and analysis effect of the EEG paradigm signal.

The buffer in the AFE is designed to enable EEG recording without signal attenuation even with high electrode-skin interface impedance (ESI) and its variation. Active shielding by buffer minimizes the parasitic capacitance and can boost the input impedance. By utilizing this, very small fine EEG signals can be received through the analog front end.

Fig. 1. Entire block diagram of the EEG measurement module.

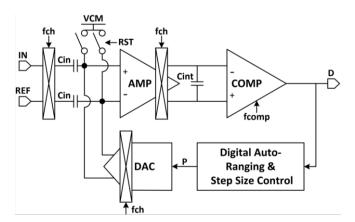

The block diagram of neural recording Bio-ADC is shown in Fig. 2. The signal is integrated using the 2nd-order open-loop Gm-C integrator. The current reuse schematic is used in the amplifier of the integrator for high energy efficiency.

Then, the dynamic comparator determines the value D which is the output sign of the comparison results by using the integrated signal. The system uses 2nd-order Delta-Sigma modulation ( $\Delta^2\Sigma$ ) ADC, enabling ADC-direct neural recording without a separate amplification process. Chopper stabilization and oversampling perform noise-shaping, which improves the signal-to-noise ratio (SNR) by eliminating low-frequency noise such as flicker (1/f) noise. In addition, with the help of digital auto-ranging and prediction block, ADC output quickly follows the input signal when it fluctuates significantly due to large artifacts.

For example, if the ADC output sign is changed three times continuously, it increases the resolution of ADC. Taking these advantages of ADC, the overall system implements a digital DC servo loop that resets the input DC point back to the original bias point when a large artifact beyond a certain specific threshold is detected. The resolution of the input ADC can be controlled for up to 8 bits depending on the amount of change in the signal.

Fig. 2. Entire circuit diagram of neural recording Bio-ADC.

### B. Stimulation Artifact Removal Algorithm

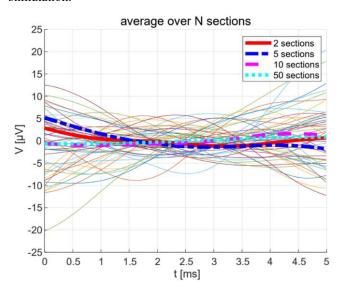

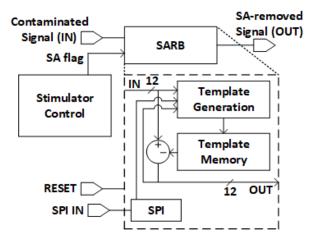

Basic assumptions behind the operation of the algorithm are as follows: 1) Neural signals can be removed by averaging throughout the time axis. (Fig 3); 2) Stimulation artifacts are identical, for at least a short period; 3) Stimulation artifacts contaminate neural signals in simple addition-based operation. The block diagram of the stimulation artifact removal algorithm is shown in Fig 4.

After reset, all parameters are set to the initial value. Parameters are changed using the SPI interface. During the operation, the stimulation artifact removal block (SARB) keeps checking whether stimulation occurs. If it recognizes stimulation, the stimulation artifact (SA) flag is turned on and maintained till the termination logic is conducted. While the SA flag is on, SARB keeps updating the artifact template for each sample. If the number of updated samples reaches the designated value, the termination logic operates and starts to wait for the next SA flag.

#### C. Charge-Balanced Stimulator

To prevent tissue damage and corrosion of electrodes, it is important to ensure the charge balance during stimulation. The stimulator uses an H-bridge structure to accomplish this design goal [10]. The H-bridge stimulator uses the same current source for both cathodic and anodic phases. Therefore, it easily makes charge-balanced biphasic stimulation.

Fig 3. Change of neural signal data during template generation. The neural signal goes to zero when more time sections are averaged.

Fig. 4. Block diagram of stimulation artifact removal algorithm.

#### III. RESULTS AND DISCUSSIONS

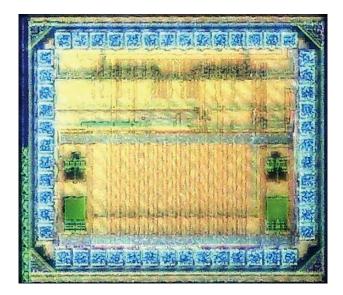

The suggested design was implemented as IC chips. The layout picture is displayed in Fig. 5. The semiconductor chips were fabricated through the TSMC 65nm LP process and the functional profiles were measured through the following process.

## A. EEG Recording AFE and ADC-Direct Neural Recording: simulations and measurements

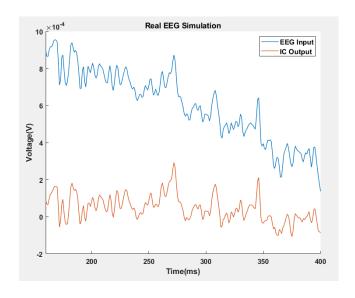

Fig. 6 shows the simulation results of the IC that the designed circuit can measure the aimed biopotential signal. The surrogate signal whose magnitude and frequency spectrum mimic EEG is applied on the IC input and the ADC provides the output with the intended DC settling profile.

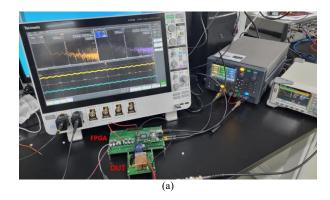

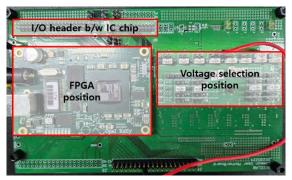

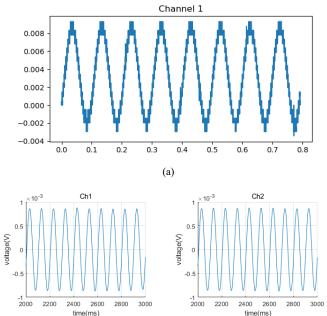

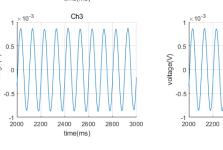

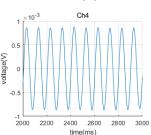

Fig. 7 shows the experiment setup and measured output signal of the buffer. In the experiment, AFE records the input signal well with negligible signal attenuation. Fig. 8 shows the ADC output results through the IC chip. It can record submV EEG magnitude signals well.

Fig. 5. Layout picture of neural stimulator with SARB.

Fig 6. Simulation results when an EEG-like signal is applied on IC input (blue). ADC shows a well-recorded output signal (orange).

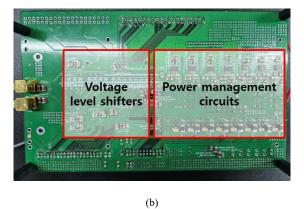

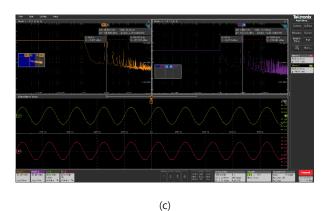

Fig 7. (a) Experiment setup for IC chip test measurement, (b) Test PCB board with FPGA, I/O header for communication with IC, voltage level shifter, and power management circuits, and (c) Input signal (green: time | orange: FFT) is recorded through the buffer and the output signal is shown (red: time | purple: FFT).

(b)

Fig 8. Output results when small signal is inserted into IC input: (a) <mV range signal can be recorded through overall IC in real-time and (b) 60Hz PLI noise is removed by postprocessing, then integrated buffer and ADC circuit can measure EEG-like magnitude signal with very low noise.

#### B. Neural Stimulation and the Artifact Removal

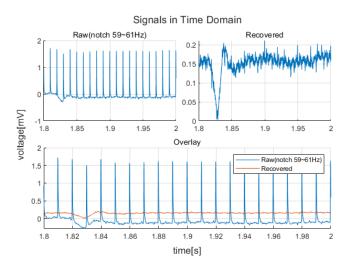

Fig. 9 shows the stimulation artifact removal result. Brain signal and stimulation artifact were recorded simultaneously by integrated ADC of the IC. Power line noise is removed by a 60Hz notch filter using MATLAB. Comparing before and after the stimulation artifact removal, clearly shows that an integrated stimulation artifact removal module can remove artifacts and recover neural signals.

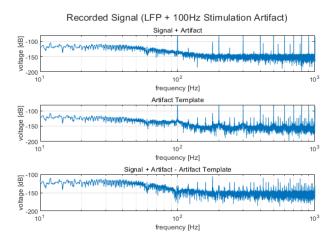

Fig. 10 shows the Fourier transform of the notch-filtered raw signal, the artifact template, and the recovered neural signal. The FFT of the template shows an undesired distortion and it appears at the FFT of the recovered signal. If this distortion is higher than the neural signal floor, the processed IC cannot be used to recover the neural signal. However, the size of the distortion is less than -120dB which is smaller than the noise floor of the signal band (10~50Hz). Therefore, it can be ignored.

Fig. 9. Time domain signal plot of the recorded neural signal. The top left and right show the raw signal and the artifact-removed signal each. The bottom shows an overlay plot of the top two signals.

Fig 10. Frequency domain signal plot. From top to bottom, each shows the recorded neural signal, the generated artifact template, and the artifact-removed signal.

TABLE I. Performance Comparison

| Performance                           | This work    | [11]          | [12]         |

|---------------------------------------|--------------|---------------|--------------|

| Process                               | 65nm<br>CMOS | Sub-µ<br>CMOS | 65nm<br>CMOS |

| Supply voltage (V)                    | 1 / 2        | 5.25          | 1.2 / 2.5    |

| Artifact suppression (dB)             | 45           | 100           | 60           |

| Input referred noise $(nV/\sqrt{Hz})$ | 237.2        | 144.6         | 126.9(3)     |

| Artifact rejection delay              | < 1s (1)     | _(2)          | < 2s         |

<sup>(1)</sup> At 100Hz stimulation frequency

#### IV. CONCLUSION

In this work, circuit systems for bio-potential recording in daily life were designed, implemented, and tested: the 4channel EEG-recording AFE with the low-noise buffer and the 2<sup>nd</sup>-order delta-sigma modulating Bio-ADC, and the digitally controlled neural stimulator with the stimulation artifact removal module by the artifact template method. Through the TSMC 65nm LP process, mm<sup>2</sup> scale IC chips are fabricated. Table I summarizes the key features compared with the performance of the prior arts. The result shows that the low-noise EEG recording AFE and ADC can read EEGmagnitude uV level signals well. The stimulation artifact removal method using artifact-template estimation by averaging method could effectively reduce artifacts from the recorded LPF. While electrical stimulations were given, the artifact profiles could be removed in the time and frequency domain.

#### ACKNOWLEDGMENT

The chip fabrication and EDA tools were supported by IC Design Education Center (IDEC), Korea.

#### REFERENCES

- [1] Smith, S. J. M. (2005). EEG in the diagnosis, classification, and management of patients with epilepsy. *Journal of Neurology, Neurosurgery & Psychiatry*, 76(Suppl. 2), ii2-ii7.

- [2] Zhigalov, A., Kaplan, A., & Palva, J. M. (2016). Modulation of critical brain dynamics using closed-loop neurofeedback stimulation. Clinical Neurophysiology, 127(8), 2882-2889.

- [3] Cho, J., Seong, G., Chang, Y., & Kim, C. (2021). Energy-efficient integrated circuit solutions toward miniaturized closed-loop neural interface systems. Frontiers in neuroscience, 15, 667447.

- [4] Yoo, S., Seong, G., Park, J., & Kim, C. (2022, October). Zero-Weight aware LSTM Architecture for Edge-Level EEG Classification. In 2022 IEEE Biomedical Circuits and Systems Conference (BioCAS) (pp. 472-476). IEEE.

- [5] Seok, D., Lee, S., Kim, M., Cho, J., & Kim, C. (2021). Motion Artifact Removal Techniques for Wearable EEG and PPG Sensor Systems [Review]. Frontiers in Electronics, 2.

- [6] Joshi, S., Kim, C., & Cauwenberghs, G. (2016). A 6.5μW/MHz charge buffer with 7-fF input capacitance in 65nm CMOS for noncontact electropotential sensing. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 63(12),1161-1165.

- [7] Kim, C., Joshi, S., Courellis, H., Wang, J., Miller, C., & Cauwenberghs, G. (2018). Sub-μVrms-noise sub-μW/channel ADC-direct neural recording with 200-mV/ms transient recovery through predictive digital autoranging. *IEEE Journal of Solid-State Circuits*, 53(11), 3101-3110.

<sup>(2)</sup> Conducted on external device

<sup>(3)</sup> Calculated from table in [12]

- [8] Dabbaghian, A., & Kassiri, H. (2023). An 8-channel ambulatory EEG recording IC with in-channel fully-analog real-time motion artifact extraction and removal. *IEEE Transactions on Biomedical Circuits and Systems*, 17(5), 999-1009.

- [9] Limnuson, K., Lu, H., Chiel, H. J., & Mohseni, P. (2015). A bidirectional neural interface SoC with an integrated spike recorder, microstimulator, and low-power processor for real-time stimulus artifact rejection. Analog Integrated Circuits and Signal Processing, 82(2), 457-470.

- [10] Vidal, J., & Ghovanloo, M. (2010, September). Towards a switched-capacitor-based stimulator for efficient deepbrain stimulation. In 2010 Annual International Conference of the IEEE Engineering in Medicine and Biology (pp. 2927-2930). IEEE.

- [11] Culaclii, S., Kim, B., Lo, Y. K., Li, L., & Liu, W., "Online artifact cancelation in same-electrode neural stimulation and recording using a combined hardware and software architecture", IEEE transactions on biomedical circuits and systems, 12(3), 601-613, 2018.

- [12] Uehlin, J. P., Smith, W. A., Pamula, V. R., Pepin, E. P., Perlmutter, S., Sathe, V., & Rudell, J. C., "A single-chip bidirectional neural interface with high-voltage stimulation and adaptive artifact cancellation in standard CMOS". *IEEE Journal of Solid-State Circuits*, 55(7), 1749-1761, 2020.

Geunchang Seong received the B.S. degree in bio and brain engineering from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Republic of Korea, in 2020 and an M.S. degree in bio and brain engineering from KAIST, in 2022. He is currently pursuing a Ph.D. degree in bio and brain engineering from KAIST. His research interests

include bio-signal processing, and integrated circuit (IC) chip design for biomedical healthcare systems.

Dongyeol Seok received the B.S. degree in bio and brain engineering (major) and science and technology policy (minor) from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Republic of Korea, in 2020 and an M.S. degree in bio and Brain engineering from KAIST in 2022. He is currently pursuing a Ph.D. degree in bio and brain engineering, at KAIST. His

research interests include EEG analog front-end, development of motion artifact-free EEG systems, and integrated circuit (IC) chip design for biomedical healthcare systems.

Minjae Kim received a B.S. degree in bio and brain engineering (major) and electrical engineering (minor) from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Republic of Korea, in 2021 and an M.S. degree in bio and brain engineering from KAIST, in 2023. He is currently pursuing a Ph.D. degree in bio and brain engineering,

KAIST. His research interests include in-ear EEG technology, the development of motion artifact removal in EEG sensors, and integrated circuit (IC) chip design for biomedical healthcare systems.

Chul Kim (Senior Member, IEEE) is an associate professor in the Department of Bio and Brain Engineering and the Program of Brain and Cognitive Engineering at Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea. He received the Ph.D. degree in bio engineering, UC San Diego,

La Jolla, CA, USA, in 2017 where he was a postdoctoral fellow from 2017 to 2019. From 2009 to 2012, he was with SK HYNIX, Icheon, South Korea, where he designed power management circuitry for dynamic random-access memory (DRAM). His current research interests include the design of energy-efficient integrated circuits and systems for fully wireless brain-machine interfaces and unobtrusive wearable sensors.