# A Photodiode Sensor Readout Circuit Utilizing a Differential Current Mirror for Dark Current Cancellation

# Haejun Noh, Woojin Kim and Hyuntak Jeon<sup>a</sup>

School of Semiconductor Engineering, Chungbuk National University E-mail: ht.jeon@cbnu.ac.kr

Abstract - This paper proposes a differential current mirror circuit with built-in dark current cancellation for photodiode applications. The photodiode sensor, modeled with a diode and a parasitic capacitor, generates a current signal that is directed through two current mirrors. The signals from each current mirror are then differentially outputted. Thanks to the proposed differential current mirrors, the only high frequency signal current can be transferred to output port effectively. The proposed sensor interface ICs were implemented using the PDK of the DB Hitek process and achieved a dark current cancellation ratio of 40 dB at a reconfigurable frequency.

Keywords—Photodiode sensor interface ICs, Dark current cancellation, Current mirrors

#### I. INTRODUCTION

Photodiodes are among the most widely used sensors, capable of detecting various factors such as light intensity and radiation to generate charge-based current signals [1]. However, photodiodes generate current not only in response to incident photons but also in the absence of light, leading to a current that can degrade the accuracy of signal processing circuits. This phenomenon is known as dark current [2]. Eliminating dark current enhances sensor accuracy, simplifies signal processing, reduces power consumption, and extends the operational lifetime of the sensor signal processing system [3–4].

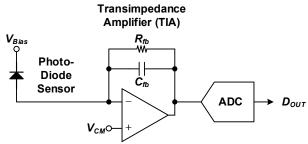

Traditional photodiode sensor signal processing systems typically consist of a photodiode, a transimpedance amplifier (TIA), and an analog-to-digital converter (ADC), as shown in Fig. 1 [5–7]. The photodiode converts incident photon particles into charge, which the TIA integrates to produce a voltage signal suitable for conversion by the ADC. Due to their operational characteristics, signals generated by photodiodes inherently include dark current. Since the TIA cannot distinguish between dark current and signal current, it must output peak voltage values for every event where current is generated.

# a. Corresponding author; ht.jeon@cbnu.ac.kr

Manuscript Received Jul. 1, 2024, Revised Sep. 2, 2024, Accepted Sep. 3, 2024

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<a href="http://creativecommons.org/licenses/by-nc/4.0">http://creativecommons.org/licenses/by-nc/4.0</a>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Fig. 1. Conventional Photodiode Sensor Interface Circuits.

#### II. DESIGN METHODOLOGY

## A. System Configuration

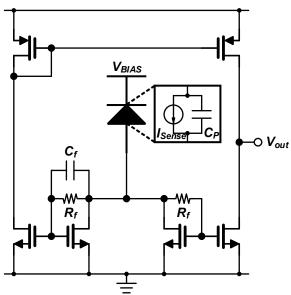

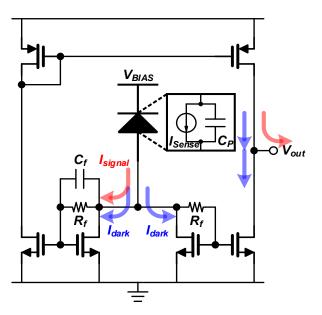

Fig. 2. Proposed Photodiode Dark Current Cancellation Circuit.

Fig. 2 illustrates the configuration of the proposed photodiode dark current cancellation circuit. The current signal generated by the photodiode is split between two current mirrors. Unlike conventional connections where the gate and drain of the MOS transistors are directly connected with a wire, each current mirror in this design utilizes a pair of resistors  $R_f$ . Additionally, the left current mirror has a capacitor  $C_f$  connected in parallel with  $R_f$ . The photodiode generates the current signal, while the two current mirrors receive and convey the current signal to the output port  $V_{out}$ .

#### B. Key Concepts

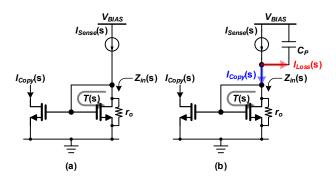

Fig. 3 (a) Schematic of the traditional current mirror circuit, (b) Schematic of the traditional current mirror circuit with the parasitic capacitance of the photodiode added.

The current mirror that receives the current signal generated by the photodiode should have low input impedance ( $Z_{in}(s)$ ) to minimize the loss of current signal transmission. The  $Z_{in}(s)$  of the current mirror described in Fig. 3(a) can be expressed as follows:

$$Z_{in} = \frac{r_o}{1 + g_m r_o} \approx \frac{1}{g_m} \tag{1}$$

The principle behind deriving the formula in (1) involves utilizing the fact that the gate and drain are connected by a feedback loop. The impedance of a circuit with feedback can be calculated by dividing the impedance of the circuit without feedback  $(r_o)$  by the loop gain  $(1+T=1+g_mr_o)$ . However, the  $Z_i$  can be relatively increased due to the parasitic capacitance  $C_P$ .  $C_P$  can be modelled as a parasitic capacitance of sensor. In this work,  $C_P$  is determined by a type of radiation sensor, the SiPM, with several nano Farad. As shown in Fig. 3(b), the increased high-frequency impedance reduces the signal current entering the current mirror, resulting in greater signal loss.

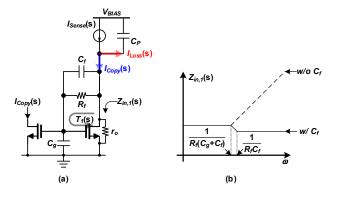

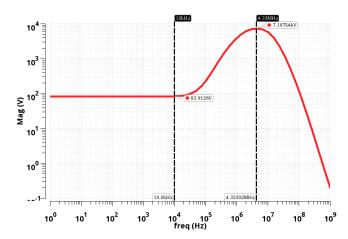

Fig. 4. Proposed low-loss current mirror (a) Detailed schematic, (b) Bode plot of the input impedance.

To overcome the high-frequency impedance issue of the traditional current mirror in Fig. 3, we propose a low- $Z_{in}(s)$  at high-frequency current mirror as shown in Fig. 4(a). By connecting an  $R_f$  and a capacitor  $C_f$  between the gate and drain of the MOS transistor, the  $Z_{in}(s)$  can be changed as

follows:

$$Z_{in,1} = \frac{1}{g_m} \cdot \frac{1 + sR_f C_f}{1 + sR_f (C_f + C_g)}$$

(2)

Fig. 4(b) shows a comparison of impedances (1) and (2) in the frequency domain using a Bode plot. The new pole created by the addition of  $R_f$  and  $C_f$  prevents impedance rise, minimizing the leakage of high-frequency current signals that could be absorbed by  $C_P$ . To utilize the proposed current mirror in photodiode sensor signal processing circuits in Fig. 2, we additionally use a current mirror with only the resistor  $R_f$  connected, without  $C_f$ . The  $Z_{in}(s)$  of the current mirror without  $C_f$  can be rederived as follows:

$$Z_{in,2} = \frac{1}{g_m} \cdot \frac{1}{1 + sR_fC_a} \tag{3}$$

Fig. 5. Conceptual diagram of the differential current mirror for removing photodiode dark current.

Thus, the current signals generated by the photodiode sensor are injected into two different current mirrors and pass through an active load circuit composed of the PMOS transistors to output a single voltage signal. The current mirror with only  $R_f$  connected blocks high-frequency current signals and only passes low-frequency current signals. The low-frequency current signal, specifically the dark current, is removed at the output stage. Fig. 5 explains the principle of dark current removal. The final transfer function of the output voltage ( $V_{out}$ ) for input current ( $I_{Sense}$ ) can be calculated as follows:

$$\frac{V_{out}}{I_{Sense}} = \left(\frac{Z_{in,2}}{Z_{in,1} + Z_{in,2}} - \frac{Z_{in,1}}{Z_{in,1} + Z_{in,2}}\right) Z_{out} \tag{4}$$

$Z_{out}$  is the output impedance of the output node  $V_{out}$ .

#### III. RESULTS AND DISCUSSIONS

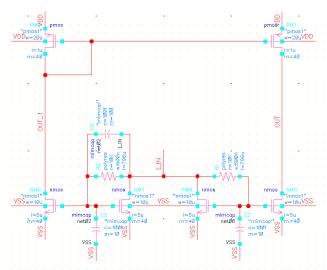

Fig. 6. Schematic of proposed photodiode sensor interface ICs.

Fig. 7. Bode plot of output voltage from input current source  $(V_{out}/I_{Sense})$ .

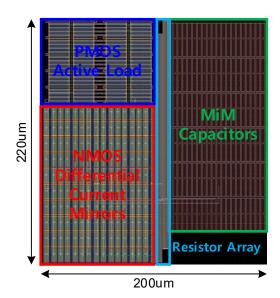

Fig. 8. Layout of proposed photo-diode sensor interface ICs.

Fig. 6. displays the schematic design results of the circuit as described above. As the values of each component in Fig. 6, 10 pF of  $C_f$ , 1 pF of  $C_g$  and 10 k $\Omega$  are used. All of the transistors are sized to satisfy the condition of 0.2 V  $V_{d,sat}$ . As shown in Fig. 7, the signal transfer function reaches a peak in the MHz range. If some current signal of photodiode is distributed over MHz, the gain of signal can be maximized. On the other hand, the low-frequency dark current signal can be filtered by the low gain over low frequency. The maximum ratio between dark current and signal current is simulated as 40 dB. The layout design of the proposed concept is shown in Fig. 8. The implemented circuit occupies an area of 0.13 mm², but it can be changed for each application.

#### IV. CONCLUSION

This paper proposes an integrated circuit for photodiode sensor interface utilizing differential current mirrors. Thanks to the differential current mirrors, the dark current from the photodiode can be cancelled effectively. In addition, this design methodology can be applied to other applications that are sensitive to dark current.

#### ACKNOWLEDGMENT

This research was supported by the research grant of the Chungbuk National University in 2022. The EDA tool was supported by the IC Design Education Center (IDEC), Korea.

### REFERENCES

- [1] X. Sun et al., "HgCdTe avalanche photodiode array detectors with single photon sensitivity and integrated detector cooler assemblies for space LiDAR applications," *Opt. Eng.*, vol. 58, no. 6, pp. 1, Jun. 2019.

- [2] L. W. Lim, C. H. Tan, J. S. Ng, J. D. Petticrew and A. B. Krysa, "Improved planar InAs avalanche photodiodes with reduced dark current and increased responsivity," *J. Lightw. Technol.*, vol. 37, no. 10, pp. 2375-2379, May 2019.

- [3] S. Dey, J. C. Rudell, T. K. Lewellen and R. S. Miyaoka, "A CMOS front-end interface ASIC for SiPM-based positron emission tomography imaging systems," *Proc. IEEE Biomed. Circuits Syst. Conf. (BioCAS)*, pp. 1-4, Oct. 2017.

- [4] A. M. Brunetti, M. Musolino, S. Strangio and B. Choubey, "Pixel design driven performance improvement in 4T CMOS image sensors: Dark current reduction and full-well enhancement," *IEEE Trans. Electron Devices*, vol. 67, no. 1, pp. 409-412, Jan. 2020.

- [5] R. Y. Chen and Z.-Y. Yang, "CMOS transimpedance amplifier for visible light communications," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 23, no. 11, pp. 2738-2742, Nov. 2015.

- [6] C.-M. Tsai, "A 40 mW 3 Gb/s self-compensated differential transimpedance amplifier with enlarged input capacitance tolerance in 0.18μm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2671-2677, Oct. 2009.

[7] M. G. Ahmed, T. N. Huynh, C. Williams, Y. Wang, P. K. Hanumolu and A. Rylyakov, "34-GBd linear transimpedance amplifier for 200-Gb/s DP-16-QAM optical coherent receivers," *IEEE J. Solid-State Circuits*, vol. 54, no. 3, pp. 834-844, Mar. 2019.

**Haejun Noh** received the B.S. degrees in electronics engineering from Chungbuk National University, Cheongju, Korea, in 2024.

He is working as a master student in Chungbuk National University and his research interests include power management and sensor interface ICs.

Woojin Kim received the B.S. degrees in electronics engineering from Chungbuk National University, Cheongju, Korea, in 2024.

He is working as a master student in Chungbuk National University and his research interests include power management and sensor interface ICs.

Hyuntak Jeon received the B.S. degree in electronic and electrical engineering from Hongik University, Seoul, South Korea, in 2015, and the M.S. and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 2017 and 2021, respectively.

He was a Senior Researcher with the Agency for Defense Development (ADD), Daejeon, from 2021 to 2022. In 2022, he joined the School of Semiconductor Engineering, Chungbuk National University, Cheongju, South Korea, where he is currently an Assistant Professor. His research interests include mixed-signal and power management IC design.