# A Low-Power, Highly Linear Sub-GHz Receiver Front-End with a Voltage Follower-Based 4<sup>th</sup>-Order Channel Selection Filter

Deok-Young Kim<sup>1</sup>, Jong-Won Park, Yaehoon Roh, Gyeore Lee, and Donggu Im<sup>a</sup>

Division of Electronic Engineering, Jeonbuk National University E-mail: ¹kdy1894@jbnu.ac.kr

Abstract - A low-power, highly linear sub-GHz receiver frontend designed for LPWAN IoT applications is presented, featuring a voltage follower-based 4th-order channel selection filter. The receiver front-end comprises a wideband single-todifferential (S-to-D) low-noise amplifier (LNA), an inphase/quadrature (I/Q) passive mixer, and the proposed advanced channel selection filter. The S-to-D LNA utilizes two cascaded inverters and a correction amplifier to achieve high gain, low noise, and high linearity while minimizing power consumption. The channel selection filter employs a novel design that combines the flipped voltage follower (FVF) and super source follower (SSF), enabling the implementation of a 4thorder filter without degrading the noise figure (NF). Implemented in 130-nm CMOS technology, the receiver achieves a conversion gain of approximately 30 dB, a doublesideband NF (NF<sub>DSB</sub>) of 3 dB at a cut-off frequency, and an output-referred third-order intercept point (OIP3) between +6.2 dBm and +7.7 dBm in the sub-GHz band, with a total power consumption of 8.9 mW from a 1.2 V supply.

Keywords - CMOS, channel selection filter, flipped voltage follower, inverter

# I. INTRODUCTION

The Internet of Things (IoT) mobile communication is moving toward high frequency bands for higher data rate, and on the other hand, it is also moving toward low frequency bands, which generally refer to the frequency band below 1 GHz, in order to ensure long transmission distance, wide scope, and good signal penetrability. This is for interconnecting a variety of devices, people, and data for a wide range of applications such as manufacturing, agriculture, commercialization, smart homes and buildings, autonomous vehicles, healthcare, and almost everywhere. In contrast to the short-range wireless communication systems such as 2.4 GHz IEEE 802.15.4 (ZigBee) and Bluetooth Low-Energy drawing little power and transferring data at a high data rate, many low-power wide-area network (LPWAN) technologies including long-range wide-area networks (LoRaWAN), narrowband-IoT (NB-IoT), and long-term evolution for machines (LTE-M) can extend the communication coverage and improve battery life [1]. These technologies occupy sub-GHz multi-ISM-bands (typically 433 or 868 MHz), and the narrowband operation of a sub-GHz radio enables transmission between 1 and 50 kilometers. Because

a. Corresponding author; dgim@jbnu.ac.kr

Manuscript Received Jun. 11, 2024, Revised Sep. 20, 2024, Accepted Sep. 25, 2024.

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<a href="http://creativecommons.org/licenses/by-nc/4.0">http://creativecommons.org/licenses/by-nc/4.0</a>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

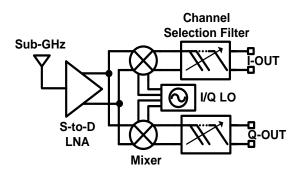

Fig. 1. Schematic of the proposed receiver front-end composed of wideband single-to-differential (S-to-D) low noise amplifier (LNA), in-phase/quadrature (I/Q) passive mixer and channel selection filter.

sensitivity is inversely proportional to channel bandwidth, a narrower bandwidth leads to higher receiver sensitivity and improved efficiency at lower transmission rates.

The sub-GHz receiver front-end should provide a higher out-of-band (OOB) rejection characteristic because of very crowded strong interference signals in the sub-GHz frequency band such as digital TV, 4G/5G cellular, 802.11ah, and other sub-GHz protocols. Especially, the requirements for the adjacent and alternative channel rejection of the sub-GHz receiver have become much more stringent. Because the adjacent and alternative channel rejection ratio are dominated by the channel selection filter, it is necessary to design of a highly linear low-noise, higher-order channel selection filter with low power consumption.

In this paper, a low-power, highly linear sub-GHz receiver front end employing a voltage follower-based 4<sup>th</sup>-order channel selection filter is proposed for LPWAN IoT applications. Especially, this work focuses on the design a highly linear low noise channel selection filter with low power consumption for high-frequency applications.

# II. REVIEW OF TRADITIONAL CHANNEL SELECTION FILTERS

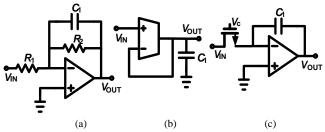

Fig. 1. shows the schematic of the proposed receiver frontend composed of a wideband single-to-differential (S-to-D) low noise amplifier (LNA), an in-phase/quadrature (I/Q) passive mixer and a channel selection filter. The continuous-time channel select filters can be implemented using active-RC, transconductance-C ( $G_m$ -C), and MOSFET-C topologies as shown in Fig. 2, with each solution presenting significant drawbacks. The active-RC topology is a promising candidate for channel selection filter owing to the excellent linearity by the negative feedback operation. It is well known that the harmonic distortion can be suppressed by an amount of the

Fig. 2. Traditional continuous-time channel selection filters: (a) active-RC filter, (b) transconductance ( $G_m$ )-C filter, (c) MOSFET-C filter.

loop gain. However, it suffers from high power consumption because the unity gain bandwidth of the operation amplifier in active-RC filter should be much higher than the cut-off frequency of the filter in order to ensure a sufficiently high open loop-gain within the operating frequency of the filter. Concerning for  $G_m$ -C filter topology, it can operate at high frequency band with low power consumption and relatively low noise performance, but its linearity is quite poor due to the transconductance nonlinearity. Many studies have tried to improve the linearity of  $G_m$ -C filter using MOSFET superposition methods [2]-[4], derivative but improvement is very sensitive to process, voltage, and temperature variations. The MOSFET-C implemented using triode region MOSFETs as voltagecontrolled resistors in the integrators, but unfortunately this severely degrades the linearity. Furthermore, as the supply voltage decreases together with channel length scaling, the threshold voltage does not reduce at the same rate, resulting in a lower frequency coverage for this filter. As a result, it is highly required to implement a low power high-frequency channel selection filter to overcome the issues of the traditional filter topologies.

# III. DESIGN OF PROPOSED LOW NOISE AMPLIFIER (LNA) AND MIXER

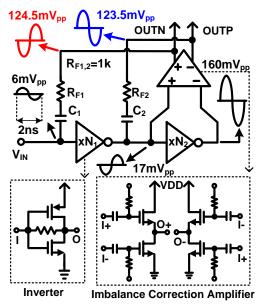

Fig. 3 presents a schematic of the proposed S-to-D LNA. The CMOS inverter with DC feedback has been widely used in the design of high-frequency amplifiers for its high gain, low noise, high linearity, and simple hardware configuration. The effective transconductance can be easily increased through the current reuse technique. As a result, the proposed LNA is built on the basis of the cascaded two inverters. A large resistor is connected between the gate and drain nodes to stabilize the DC operating point. The drain node voltage of the inverter is biased at half the supply voltage in order to provide the largest output voltage swing and high linearity. The value of the DC feedback resistor between the gate and drain nodes of inverter is 50 k $\Omega$ . This large resistance is implemented using a high-sheet-resistance polysilicon resistor provided by the commercial process design kit (PDK). On the other hand, the simulated input common-mode range of the inverter ranges from 570 mV to 620 mV.

The cascaded inverters provide the single-to-differential conversion to exclude the use of the bulky off-chip transformer in sub-GHz band. However, the amplitude imbalance is inevitable in the cascaded inverters. To compensate these amplitude and phase imbalances, two single-ended outputs of two cascaded inverters are applied to the imbalance correction amplifier, which is a combined topology of the differential common-source amplifier and a source follower.

Fig. 3. The proposed wideband inverter-based single-to-differential (S-to-D) LNA. The voltage swing waveform at each node is shown when a 500 MHz RF signal with a power of -40 dBm is applied to the LNA.

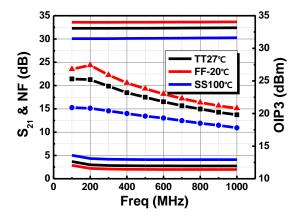

Fig. 4. The simulated power gain  $(S_{21})$ , NF and output-referred third-order intercept-point (OIP3) of the proposed LNA against process corner and temperature variations. The symbol 'T', 'F', and 'S' stand for the typical, fast, and slow model, respectively.

On the other hand, the resistive or source follower feedback is very effective technique for wideband input impedance matching. To implement a wideband active feedback S-to-D LNA, two feedback resistors  $(R_F)$  are connected between the input of the first (second) inverter and the non-inverting output OUTP (inverting output OUTN) of the correction amplifier, respectively. This configuration ensures the identical loading conditions for the differential output (OUTN and OUTP) of the correction amplifier, thereby minimizing the imbalances with low power consumption. As shown in the voltage swing levels at each node in the proposed LNA, most of the voltage gain is achieved through the second inverter stage. In the open-loop state (without  $R_{F1}$  and  $R_{F2}$ ), the voltage gains of the first and second inverter stages is approximately 16.7 dB (xN<sub>1</sub>) and 21.7 dB ( $xN_2$ ) respectively. The transconductance ( $g_m$ ) value of the common source (CS) and source follower (SF) transistors in the imbalance correction amplifier are the same, implying the voltage gain through the CS and SF stages is almost identical for a specific value of the feedback resistor.

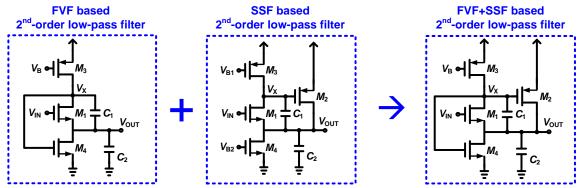

Fig. 5. The 2<sup>nd</sup>-order low-pass filter combining a flipped voltage follower (FVF) based version and a super source follower (SSF) based version [12].

Fig. 6. Proposed 4th-order channel selection filter.

On the other hand, the loop gain and voltage gain of the proposed LNA are expressed as:

$$T_{LOOP} \approx (N_1 + N_1 N_2)$$

and (1)

$$A_V \approx \frac{2R_F}{R_S} \frac{T_{Loop}}{1 + T_{Loop}} \approx \frac{2R_F}{R_S} \ . \tag{2} \label{eq:average}$$

When negative feedback is applied to the open loop amplifier, the harmonic distortions are reduced by a factor of the loop gain, and the relationship between input-referred third-order intercept point (IIP3) of the open-loop and closed-loop amplifiers is given by:

$$IIP3_{Closed-Loop} \approx IIP3_{Open-Loop} \times (1 + T^*_{LOOP})^{3/2}$$

(3)

where IIP3<sub>Closed-Loop</sub> and IIP3<sub>Open-Loop</sub> denote IIP3 of the closed- and open-loop amplifier, respectively [5].  $T^*_{LOOP}$  is the loop gain when the input of the LNA is terminated with the source impedance  $R_S$ . In comparison with the conventional resistive or source follower feedback LNAs in [6]-[9], the proposed LNA shows the lower noise figure (NF) and higher linearity due to the enhanced loop gain. Fig. 4. presents the simulated power gain  $(S_{21})$ , NF, output-referred third-order intercept-point (OIP3) of the proposed LNA across process corner and temperature variations. The symbol 'T', 'F', and 'S' stand for the typical, fast, and slow model, respectively. The S<sub>21</sub> and NF range from 30 dB to 33.5 dB and from 2 dB to 4.1 dB, respectively. The OIP3 ranges from +19.7 dBm to 23.8 dBm in the 500 MHz frequency band. For the mixer, the current communicating passive mixer is employed for high linearity.

#### IV. DESIGN OF PROPOSED CHANNEL SELECTION FILTER

The source follower-based filters show better performance than op amp-based filters in the aspects of gain bandwidth, linearity and power dissipation. As is well known, the flipped voltage follower (FVF) [10] and the super source follower (SSF) [11] are improved versions of the conventional source follower, which have better linearity and unity-gain bandwidth under the same power dissipation. The proposed channel selection filter is designed on the basis of the more advanced source follower reported in [12], which combines FVF and SSF as shown in Fig. 5. Two feedback paths ( $M_2$ and  $M_4$ ) increase the loop gain, and, as a result, enhance the effective transconductance  $(g_{m1})$  of the input transistor  $M_1$ . This improves the noise performance of the filter. In other words, the dual loop configuration using both  $M_2$  and  $M_4$  can have larger loop gain than the single loop configuration using only  $M_4$  because the overall loop gain by the dual loop is given by the product of each loop gain. In addition, the current consumed by  $M_2$  can be re-used by  $M_4$ . Since the FVF+SSF structure has a larger number of nodes to connect than FVF, it is easier to design a higher-order filter.

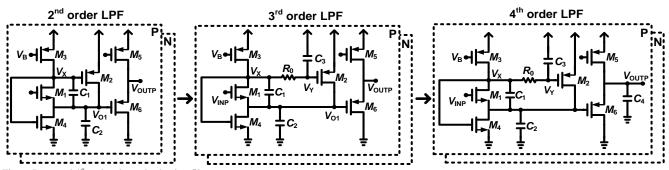

The schematic of the complete FVF+SSF based  $2^{nd}$ -order low-pass filter is shown in Fig. 6. The source follower stage composed of transistors  $M_5$  and  $M_6$  is added to shift the DC level of the output voltage and match the DC level with the next building block. In addition, it is useful to implement a higher-order filter by simply connecting the capacitor to its output. The transfer function of the proposed filter is calculated as:

$$H(s) \approx \frac{1}{s^2 \frac{C_1 C_2}{g_{m1}(g_{m2} + g_{m4})} + s \frac{C_1}{g_{m1}} + 1},$$

(4)

where  $g_{mi}$  is the transconductance of the transistor  $M_i$ . From Eq. (4), the cut-off frequency  $(\omega_0)$  and quality factor (Qfactor) of the filter is given as:

$$\omega_0 \approx \sqrt{\frac{g_{m1}(g_{m2} + g_{m4})}{C_1 C_2}} \text{ and } Q \approx \sqrt{\frac{C_2 g_{m1}}{C_1 (g_{m2} + g_{m4})}}.$$

(5)

On the other hand, the output-referred noise voltage  $(V_{n,o})$ of the 2<sup>nd</sup>-order low-pass filter is calculated as:

$$\overline{V_{n,o}^2} = \sum_{i=1}^6 \left| H_{n,Mi}^2 \right| \cdot \overline{i_{n,Mi}^2} \,, \tag{6}$$

where  $H_{n,Mi}$  is the transfer function of the output voltage from the current noise  $i_{n,Mi}$  of each transistor  $M_i$ . The  $H_{n,Mi}$ of each transistor  $M_i$  is given as:

$$H_{n,M1} \approx \frac{g_{m2} + g_{m4}}{s^2 C.C_2 + s C.(g_2 + g_3) + g_3(g_2 + g_3)},$$

(7)

$$H_{n,M1} \approx \frac{g_{m2} + g_{m4}}{s^2 C_1 C_2 + s C_1 (g_{m2} + g_{m4}) + g_{m1} (g_{m2} + g_{m4})},$$

(7)

$$H_{n,M2,4} \approx \frac{s C_1}{s^2 C_1 C_2 + s C_1 (g_{m2} + g_{m4}) + g_{m1} (g_{m2} + g_{m4})},$$

(8)

$$H_{n,M3} \approx \frac{sC_1 - (g_{m2} + g_{m4})}{s^2 C_1 C_2 + sC_1 (g_{m2} + g_{m4}) + g_{m1} (g_{m2} + g_{m4})}, \quad (9)$$

$$H_{n,M5} \approx \frac{1}{g_{m5}}$$

, and  $H_{n,M6} \approx \frac{1}{g_{m6}}$ . (10)

Because the channel bandwidth is quite wide and the channel length of all transistors is set to be 0.6-µm in order to minimize the effect of the flicker noise, the thermal noise is only considered for the noise calculation. As a result, the square of  $i_{n,Mi}$  is approximately given by  $4kT\gamma g_{mi}$ , where k is the Boltzmann constant, T is the absolute temperature, and  $\gamma$ is the bias-dependent channel thermal noise coefficient of the MOSFET device. In conclusion, the output-referred noise voltage of Eq. (6) at a low frequency band around DC can be simplified as:

$$\overline{V_{n,o}^2} \approx \frac{4kT\gamma}{g_{m1}} + \frac{4kT\gamma g_{m3}}{g_{m1}^2} + \frac{4kT\gamma g_{m5}}{g_{m6}^2} + \frac{4kT\gamma}{g_{m6}}.$$

(11)

One interesting thing is that the thermal noise contributions from transistors  $M_2$  and  $M_4$  are almost zero at the output as the operating frequency is close to DC because of the bandpass characteristic of  $H_{n, M2}$  and  $H_{n, M4}$ . In order to reduce  $V_{n,o}$ and achieve a NF of the filter, it is desirable to increase  $g_{m1}$ and  $g_{m6}$  and decrease  $g_{m3}$  and  $g_{m5}$ .

As shown in Fig. 6, the proposed 3<sup>rd</sup> and 4<sup>th</sup>-order low-pass filters are designed on the basis of the 2<sup>nd</sup>-order low-pass filter without the use of extra transistors and power consumption. In case of the 3<sup>rd</sup>-order low-pass filter, it is easily built by adding  $R_0$  and  $C_3$  to the core of the 2<sup>nd</sup>-order low-pass filter. On the other hand, the 4th-order low-pass filter is easily designed by adding  $C_4$  to the core of the 3<sup>rd</sup>-order low-pass filter. An interesting point is that the output-referred noise voltage of the 3rd- and 4th-order low-pass filters at a low frequency band around DC is the same as that of the 2<sup>nd</sup>-order low pass filter. This is because the thermal noise contributions from transistors  $M_2$  and  $M_4$  and resistor  $R_0$  at a low frequency band around DC become almost zero at the output because of the band-pass characteristic. In the

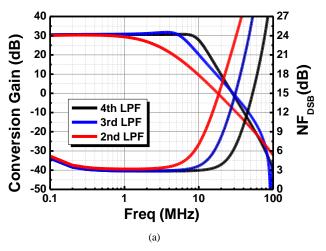

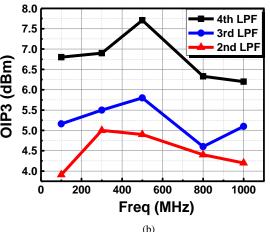

Fig. 7. Simulation results of the proposed receiver employing the 2<sup>nd</sup>-, 3<sup>rd</sup>-, and 4th-order low pass filter: (a) conversion gain and double-sideband noise figure (NF<sub>DSB</sub>), (b) OIP3.

simulation, the degradation of NF is about 3 dB at a cut-off frequency of 6 MHz when the  $R_0$  and  $C_3$  are moved to the  $V_{o1}$ node to implement 3<sup>rd</sup>-order filter. In addition, the effect of  $C_4$  can be ignored at a low frequency band around DC. In conclusion, the NF of the proposed 2<sup>nd</sup>, 3<sup>rd</sup>, and 4<sup>th</sup>-order lowpass filters in the passband is almost the same. This implies that the proposed 4th-order channel selection filter can achieve lower NF and higher linearity with lower power consumption than the conventional active-RC or  $G_m$ -C filters with the same filter order.

# V. SIMULATION RESULTS

Fig. 7. presents the simulated conversion gain, doublesideband noise figure (NF<sub>DSB</sub>), and OIP3 of the proposed receiver employing the 4th-order low pass filter. It is designed and simulated using a 130-nm CMOS technology. The power consumption of the proposed receiver, excluding the local oscillator (LO) generation circuit, is approximately 8.9 mW from a 1.2 V supply voltage. The cut-off frequency of the proposed 4<sup>th</sup>-order channel selection filter is set equal to about 10 MHz, and the receiver employing it achieves the simulated conversion gain of about 30 dB and NF<sub>DSB</sub> of 3 dB at a cutoff frequency. The simulated OIP3 ranges from 6 dBm to 8 dBm in sub-GHz band. For comparison, the simulation results of the receiver adopting the 2<sup>nd</sup>- and 3<sup>rd</sup>-order low pass filter of Fig. 6 are plotted together in Fig. 7. Note that the

[13] [14] [15] \*This work Frequency Range 0.05-0.7 0.2 - 10.3-0.8 0.1 - 1Conversion Gain 26.5 44.4-50.5 28 30 (dB) < 4.25 4.4-5.7 < 4.2 3 NF<sub>DSB</sub> (dB) In-band OIP3 12 14 27.5 6.2-7.7 @300MHz @400MHz (dBm) Filter order 4 N-path 2 4 33.6 8.7 8.9 Power(mW) @1.2V @1.2V @1.2V @1.2V CMOS 130 65 65 130 Technology(nm)

TABLE I. PERFORMANCE SUMMARY AND COMPARISON WITH PREVIOUSLY REPORTED STUDIES

proposed receiver with 4<sup>th</sup>-order low pass filter shows an almost the same in-band noise and OIP3 performances in spite of higher order of filter.

TABLE I compares the performance of the proposed sub-GHz receiver to that reported in previous works. Compared to [13], it achieves higher conversion gain and lower NF with lower power consumption.

## VI. CONCLUSION

The low-power low-noise sub-GHz receiver employing a voltage follower-based 4<sup>th</sup>-order channel selection filter is designed using 130-nm CMOS technology for LPWAN IoT applications. The proposed 4<sup>th</sup>-order channel selection filter achieved a cut-off frequency of about 10 MHz with lower NF than the traditional active-RC and  $G_m$ -C filter topologies, while consuming a lower power. The receiver showed a total double-sideband NF of around 3 dB eliminating an expensive off-chip balun in the sub-GHz band due to the proposed wideband feedback-based single-to-differential LNA.

# ACKNOWLEDGEMENT

This work was supported by a grant from the National Research Foundation of Korea (NRF) funded by the Korean government (MSIT) (No. 2022R1A2C2011267) and also by the Institute of Information & Communications Technology Planning & Evaluation(IITP)-Innovative Human Resource Development for Local Intellectualization program grant funded by the Korea government(MSIT)(IITP-2024-RS-2024-00439292). This chip fabrication and EDA tool were supported by the IC Design Education Center (IDEC), Korea.

## REFERENCES

- [1] N. Jovalekic, V. Drndarevic, I. Darby, M. Zennaro, E. Pietrosemoli and F. Ricciato, "LoRa Transceiver With Improved Characteristics," in *IEEE Wireless Communications Letters*, vol. 7, no. 6, pp. 1058-1061, Dec. 2018.

- [2] K. Kwon, H. -T. Kim and K. Lee, "A 50–300-MHz Highly Linear and Low-Noise CMOS  $G_m$  C Filter Adopting Multiple Gated Transistors for Digital TV Tuner ICs," *in IEEE Transactions on Microwave Theory and Techniques*, vol. 57, no. 2, pp. 306-313, Feb. 2009.

- [3] Shin-Jye Hsu, Che-Yu Lu and C. -C. Hung, "40MHz Gm-C filter with high linearity OTA for wireless applications," *Proceedings of Technical Program of 2012 VLSI Design, Automation and Test*, Hsinchu, Taiwan, 2012, pp. 1-4.

- [4] A. R. Ghasemi, H. Aminzadeh and A. Ballo, "Ladder-Type Gm-C Filters With Improved Linearity," in *IEEE Access*, vol. 11, pp. 41503-41513, 2023.

- [5] D. Im, H. Kim and K. Lee, "A Broadband CMOS RF Front-End for Universal Tuners Supporting Multi-Standard Terrestrial and Cable Broadcasts," in IEEE Journal of Solid-State Circuits, vol. 47, no. 2, pp. 392-406, Feb. 2012.

- [6] Jing-Hong Conan Zhan and S. S. Taylor, "A 5GHz resistive-feedback CMOS LNA for low-cost multistandard applications," 2006 *IEEE International Solid State Circuits Conference* - Digest of Technical Papers, San Francisco, CA, USA, 2006, pp. 721-730

- [7] J. Borremans, P. Wambacq, C. Soens, Y. Rolain, and M. Kuijk, "Low-area active-feedback low-noise amplifier design in scaled digital CMOS," *IEEE J. Solid-State Circuits*, vol. 43, no. 11, pp. 2422–2433, Nov. 2008.

- [8] J.-Y. Park, J.-Y. Lee, C.-K. Yeo, and T.-Y. Yun, "Analysis and optimization of a resistive-feedback inverter LNA," *Microw. Opt. Technol. Lett.*, vol. 60, no. 5, pp. 1143–1151, May 2018.

- [9] B. Guo, J. Gong and Y. Wang, "A Wideband Differential Linear Low-Noise Transconductance Amplifier With Active-Combiner Feedback in Complementary MGTR Configurations," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 1, pp. 224-237, Jan. 2021.

- [10] M. De Matteis and A. Baschirotto, "A biquadratic cell based on the flipped-source-follower circuit," *IEEE Trans. Circuits Syst. II, Exp.Briefs*, vol. 64, no. 8, pp. 867–871, Aug. 2017.

- [11] M. De Matteis, A. Pezzotta, S. D'Amico, and A. Baschirotto, "A 33 MHz 70 dB-SNR super-source-follower-based low-pass analog filter," *IEEE J. Solid-State Circuits*, vol. 50, no. 7, pp. 1516–1524, Jul. 2015.

- [12] S. Jeong, D. Kim, I. -Y. Lee and D. Im, "An Analog Baseband Spectrum Sensing Circuit Employing Voltage Follower-Based Multiorder Channel Selection Filters," in *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 69, no. 12, pp. 4714-4718, Dec. 2022.

- [13] D. Kim and D. Im, "A Reconfigurable Balun-LNA and Tunable Filter With Frequency-Optimized Harmonic Rejection for Sub-GHz and 2.4 GHz IoT Receivers," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 69, no. 8, pp. 3164-3176, Aug. 2022.

- [14] D. Kim, D. Kim, I. Llamas-Garro and D. Im, "A Sub-GHz/2.4 GHz Highly Selective Reconfigurable RF Front-End Employing an N-Path Complementary Balun-LNA and Linearized RF-to-BB Current-Reuse Mixer," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 71, no. 1, pp. 147-159, Jan. 2024.

- [15] Z. Ru, E. A. M. Klumperink, C. E. Saavedra, and B. Nauta, "A 300–800 MHz tunable filter and linearized LNA applied in a low noise harmonic-rejection RF-sampling receiver," IEEE J. Solid-State Circuits, vol. 45, no. 5, pp. 967–978, May 2010.

<sup>\*:</sup> Simulation results

**Deok-Young Kim** received the B.S. degree from the Division of Electronic Engineering at Jeonbuk National University (JBNU), Jeonju, South Korea, in 2024, where he is currently pursuing the M.S. degree. His research during M.S. course has focused on low-power IoT CMOS front-end circuit design, such as wideband low-noise amplifiers (LNAs).

Jong-Won Park received the B.S. degree from the Division of Electronic Engineering at Jeonbuk National University (JBNU), Jeonju, South Korea, in 2024, where he is currently pursuing the M.S. degree. His research during M.S. course has focused on low-power IoT CMOS front-end circuit design, such as highly linear RF filters.

Yaehoon Roh received the B.S. degree from the Division of Electronic Engineering at Jeonbuk National University (JBNU), Jeonju, South Korea, in 2023, where he is currently pursuing the M.S. degree. His research during M.S. course has focused on time delay cells such as reconfigurable sub-GHz inductor-less time delay cells in CMOS.

**Gyeore Lee** received the B.S. and M.S. degrees from the Division of Electronic Engineering at Jeonbuk National University (JBNU), Jeonju, South Korea, in 2021, and 2023, respectively, where he is currently pursuing the Ph.D. degree with the Division of Electronic Engineering. His research during Ph.D. course has focused on the RF switches, touch sensors ROICs

and spectrum sensing based on mixer first.

Donggu Im received the B.S., M.S., and Ph.D. degrees in electrical engineering and computer science from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2004, 2006, and 2012, respectively. From 2006 to 2009, he was an Associate Research Engineer with LG Electronics, Seoul, Korea, where he

was involved in the development of universal analog and digital TV receiver ICs. From 2012 to 2013, he was a Post-Doctoral Researcher with KAIST, where he was involved in the development of the first RF SOI CMOS technology in Korea with SOI business team in National NanoFab Center (NNFC), Daejeon, Korea. In 2013, he joined the Texas Analog Center of Excellence (TxACE), Department of Electrical Engineering, University of Texas at Dallas, as a Research Associate, where he developed ultra-low-power CMOS radios with adaptive impedance tuning circuits. In 2014, he joined the Division of Electronic Engineering, Jeonbuk National University, Jeollabuk-do, Korea, and is

now a professor. His research interests are CMOS analog/RF/mm-wave ICs and system design.