# Floating Gate Radiation Sensor Interface ICs with Regulated-Cascode Current Reference and Time-Based Quantizer

Woojin Kim<sup>1</sup>, Haejun Noh<sup>1</sup>, Sungkeun Yoo<sup>2</sup> and Hyuntak Jeon<sup>1,a</sup>

<sup>1</sup>School of Semiconductor Engineering, Chungbuk National University

<sup>2</sup>KBIOHealth, Osong Medical Innovation Foundation

E-mail: ht.jeon@cbnu.ac.kr

Abstract - This paper proposes power-efficient ICs for measuring the signal of a Floating Gate (FG) radiation sensor. The ICs include the function of converting the current signal generated in the FG into a digital signal through a regulated-cascode current reference (RCCS) and a time-based quantizer. The proposed sensor interface ICs are implemented with the PDK of DB Hitek process, securing a 45 dB SNR with only 14.7  $\mu W$  power consumption.

Keywords—Radiation Sensor Interface ICs, Floating Gate radiation sensor, Time-based quantizer

### I. INTRODUCTION

Radiation detection electronic systems reported to date are broadly classified into two main types. The first type utilizes traditional radiation detectors [1], which feature large volumes and high accuracy due to the use of radiation sensors requiring high operating voltages. The second type consists of modular radiation detectors [2], which utilize radiation sensors requiring relatively low operating voltages, leading to smaller sizes but lower resolution.

Recently, to overcome the drawbacks of photodiode-based radiation detection systems, integrated circuits for FG-based radiation sensor interfaces have been proposed [3]. FG-based radiation sensors exploit the Total Ionizing Dose (TID) effect [4], associated with changes in semiconductor device performance (such as Vth variation, leakage current, etc.), to convert radiation particles into light signals, eliminating the need for bulky scintillators.

FG-based radiation detection systems operate by detecting the leakage current generated in the FG. The FG-based radiation detection system proposed in [3] measures the oscillation frequency per unit time of the clock signal outputted from the oscillator by inputting the current signal generated in the FG into a current-controlled oscillator. However, such FG-based radiation detection systems suffer

from issues such as counter overflow and high-power consumption.

In this paper, we propose overcoming the drawbacks outlined in [3] by utilizing a time-based quantizer based on a differential phase detector, ensuring low power consumption and high resolution with 1st order noise shaping performance.

### II. DESIGN METHODOLOGY

## A. System Configuration

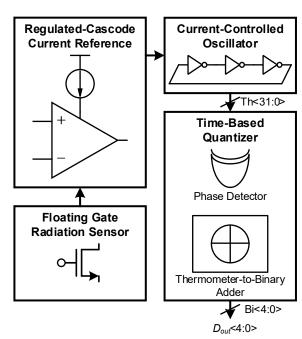

Fig. 1. System configuration of proposed FG radiation sensor interface ICs

Fig. 1. depicts the architecture of the FG-based radiation sensor interface ICs proposed in this study. The FG radiation sensor, modeled as a resistor, is designed to vary its value due to radiation particles, and it modulates the current value determined by the feedback loop of the regulated-cascode current reference circuit. The modulated current signal alters the phase of the current-controlled oscillator (CCO), which

Manuscript Received May 13, 2024, Revised Aug. 6, 2024, Accepted Aug. 13, 2024

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<a href="http://creativecommons.org/licenses/by-nc/4.0">http://creativecommons.org/licenses/by-nc/4.0</a>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

a. Corresponding author; ht.jeon@cbnu.ac.kr

is then detected by the Phase Detector (PD) consisting of D Flip-Flops (D FFs) and XOR gates.

The cascaded D FFs and PD result in quantization noise shaping to the 1st order during the process of generating the difference between the previous and current phases [5]. This prevents an increase in output bit count, resolution, and power consumption by avoiding the escalation of the number of PD arrays. In this study, 31 thermometer bits are outputted from 31 PD arrays at a 1 MHz sampling clock, and after passing through an adder, 5 binary bits are generated as output.

### B. Detailed Implementation

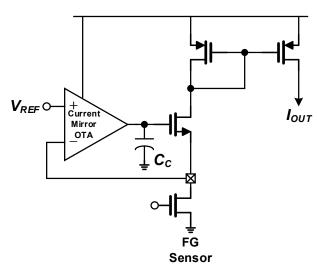

Fig. 2. Schematic of regulated-cascode current reference for FG radiation sensor

Fig. 2. illustrates the circuit diagram of the RCCS designed in this study. The FG-based radiation sensor, modeled as a resistor RFG, assumes a variable range of 0.9 Mohm to 1.1 Mohm, designed to vary the current from 0.9  $\mu A$  to 1.1  $\mu A$ . The bandwidth of the radiation signal is set to 1 kHz, while the bandwidth of the internal feedback loop gain of the RCCS is designed to be 100 kHz. The RCCS consumes an average power of 12.9  $\mu W$  and ensures sufficient linearity to transmit signals generated from the FG sensor to the CCO.

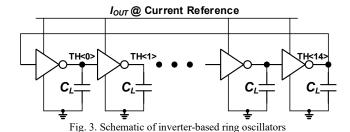

Fig. 3. presents the implementation results of the ring oscillator-based CCO composed of 31 stages. The oscillation frequency of the CCO is set to 100 kHz, and it is designed to detect the output value of the CCO at each rising edge of the 1 MHz sampling clock.

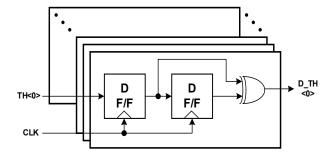

Fig. 4. Schematic of phase detector circuit with cascaded D flip-flops

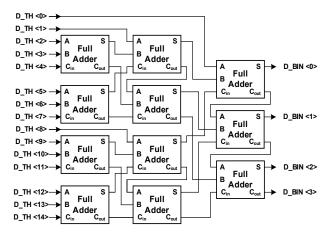

Fig. 5. Schematic of thermometer-to-binary adder

Fig. 4. displays the implementation results of the PD circuit consisting of two cascaded D FFs and XOR gates. The 31 thermometer bits detected from the PD arrays connected to the outputs of 31 CCOs represent a 5-bit binary digital output. Fig. 5. illustrates the implementation results of the adder for summing up the thermometer outputs to produce a binary 5-bit output. The implemented quantizer shown in Fig. 4. to 5. operates at 1 MHz and is simulated to consume  $1.8\ \mu W$  of power.

# III. RESULTS AND DISCUSSIONS

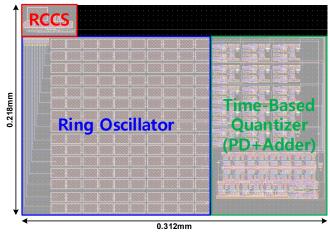

Fig. 6. Layout of proposed FG radiation sensor interface ICs

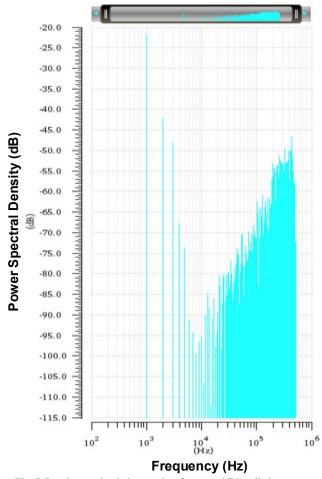

Fig. 7. Post layout simulation results of proposed FG radiation sensor interface ICs

Fig. 6. shows the layout design results of the circuit described earlier. The implemented circuit occupies an area of 0.068 mm², and the post-layout simulation results (Fig. 7.) confirm an SNR of 45 dB for the quantizer. However, it should be noted that while the SNR is 45 dB, the SNDR is significantly lower at 25 dB. The cause of this low SNDR is attributed to linearity issues in the CCO, which will be addressed through digital backend calibration.

### IV. CONCLUSION

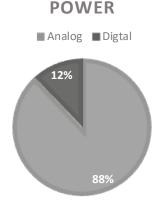

Fig. 8. Power breakdown

TABLE I. Performance Summary

| Parameters         | This Work            |

|--------------------|----------------------|

| Process            | 0.18um BCDMOS        |

| Area               | $0.0680 \text{mm}^2$ |

| Fosc of CCO        | 100kHz               |

| Sampling Frequency | 1MHz                 |

| SNR                | 45dB                 |

| Power Consumption  | 14.657uW             |

This paper proposes an integrated circuit for FG-based radiation sensor interface utilizing RCCS, CCO, and time-based quantizer. As shown in Fig. 8, the total power consumption was 14.7  $\mu$ W, with analog occupying 88% and digital occupying 12%. Although a relatively high level of SNR (45 dB) was achieved, improvements are necessary due to the low linearity.

### ACKNOWLEDGMENT

This research was supported by Chungbuk National University Korea National University Development Project (2023). The EDA tool was supported by the IC Design Education Center (IDEC), Korea.

### REFERENCES

- [1] G. L. Montagnani et al., "GAMMA: an 8-channel high dynamic range ASIC for SiPM-based readout of large scintillators," in *Proc. IEEE Nuclear Science Symp. and Medical Imaging Conf. (NSS/MIC)*, 2017.

- [2] Y. Ishigaki et al., "Development of mobile radiation monitoring system utilizing smartphone and its field tests in Fukushima," *IEEE Sensors J.*, vol. 13, no. 10, pp. 3520–3526, Oct. 2013.

- [3] B. Chatterjee *et al.*, "A wearable real-time CMOS dosimeter with integrated zero-bias floating gate sensor and an 861-nw 18-bit energyresolution scalable time-based radiation to digital converter," *IEEE J. Solid-State Circuits*, vol. 55, no. 3, pp. 650–665, Mar. 2020.

- [4] H. J. Barnaby, "Total ionizing dose effects in modern CMOS technologies," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 6, pp. 3103–3121, Dec. 2006.

- [5] P. Prabha et al., "A highly digital VCO-based ADC architecture for current sensing applications," *IEEE J. Solid-State Circuits*, vol. 50, no. 8, pp. 1785–1795, Aug. 2015.

Woojin Kim received the B.S. degrees in electronics engineering from Chungbuk National University, Cheongju, Korea, in 2024.

He is working as a master student in Chungbuk National University and his research interest includes power management and sensor interface ICs.

Haejun Noh received the B.S. degree in electronics engineering from Chungbuk National University, Cheongju, Korea, in 2024.

He is working as a master student in Chungbuk National University and his research interest includes power management and sensor interface ICs.

Sungkeun Yoo received B.S. degrees in biochemical engineering and electrical engineering from Chonnam National University, Gwangju, South Korea, in 2003, and the M.S. and Ph.D. degrees in the Department of Mechatronics, Gwangju Institute of Science and Technology (GIST), Gwangju, South Korea in 2004 and 2009, respectively. He was a Visiting

Scientist in the Bioelectronics Group at Biomaterials Center of National Institute for Materials Science (NIMS), Japan in 2006. He joined Samsung Electronics from 2010 to 2012 as a Principal Researcher. In 2012, he moved to the Medical Device Development Center, KBIOHealth (Osong Innovation Foundation), Cheongju, South Korea, where he is currently a Principal Researcher. His research interests include biosensors, bioelectronics, biomicroelectromechanical systems (bioMEMS), microfluidics, lab-on-a-chip, and surface chemistry.

Hyuntak Jeon received the B.S. degree in electronic and electrical engineering from Hongik University, Seoul, South Korea, in 2015, and the M.S. and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 2017 and 2021, respectively.

He was a Senior Researcher at the Agency for Defense Development (ADD), Daejeon, from 2021 to 2022. In 2022, he joined the School of Semiconductor Engineering, Chungbuk National University, Cheongju, South Korea, where he is currently an Assistant Professor. His research interests include mixed-signal and power IC design.