# A 28-GHz CMOS Power Amplifier with Ribbon Cell

## Younseok Han<sup>1</sup>, Seungchan Lee<sup>2</sup>, Dong-Ho Lee<sup>3</sup> and Gwanghyeon Jeong<sup>a</sup>

<sup>1</sup>Department of Intelligent Nano Semiconductor Engineering, Hanbat National University

<sup>2</sup>Department of Electronics Engineering, Chonnam National University

<sup>3</sup>Department of Mobile Convergence Engineering, Hanbat National University

<sup>a</sup>Department of Semiconductor System Engineering, Hanbat National University

E-mail: <sup>a</sup>gh.jeong@hanbat.ac.kr

Abstract - In this paper, we present a ribbon cell CMOS power amplifier in which the structure of the power cell is like a ribbon. As the frequency increases, the output impedance decreases due to parasitic capacitors, so an interstage inductor is used. The interstage inductor used in previous research has the problem of increasing the size of the chip. Ribbon cells use larger interstage inductors through mutual inductance. Therefore, a metal smaller than the desired inductor metal size can be used. This allows the chip size to be designed to be small. It also improves AM-PM distortion and IMD3. It operates at 28 GHz with a 2.4 V supply voltage and achieves IMD3 of -40dBc at 10 dBm output power and -30dBc at 12.3 dBm output power and PAE of 19% and 25% respectively. It has a saturated output power of 18.4dBm and achieves a gain of 11.6dB at a P1dB of 16.4dBm.

### Keywords—28GHz, AM-PM, CMOS, IMD3, PA

## I. INTRODUCTION

Recently, with the development of the Internet of Things (IoT), various types of IoT communication networks are being used, such as smart factories, smart buildings, smart homes, and smart farms. The e-UM 5G application using the 28GHz band supports IoT systems, and a 28 GHz transceiver is required to configure the network, as everything needs to be transmitted and received to communicate. In addition, since communication is performed based on a battery, low power consumption and miniaturization are essential. Therefore, a single-chip transceiver using the CMOS process is suitable.

When developing a single-chip transceiver using the CMOS process, linearization techniques are essential because it is very difficult to secure the linearity of the power amplifier due to the nonlinearity of the transistor. Existing researched techniques include adaptive bias circuits, structures that minimize capacitance changes with additional bias voltage, and Digital Pre-Distortion (DPD) [1-5]. The above linearization techniques have the disadvantage of requiring additional passive elements and circuit

Manuscript Received Nov. 24, 2023, Revised May 15, 2024, Accepted May 20, 2024

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<a href="http://creativecommons.org/licenses/by-nc/4.0">http://creativecommons.org/licenses/by-nc/4.0</a>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

connections, resulting in additional area. Therefore, in this paper, we designed a CMOS power amplifier using the Ribbon Cell linearization technique that minimizes the chip area and does not use additional power.

#### II.CMOS PA WITH RIBBON CELL CIRCUIT DESIGN

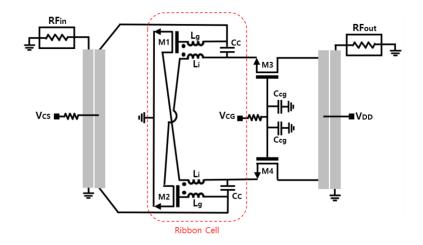

Figure 2 shows the schematic of the proposed CMOS power amplifier. Power amplifiers with a ribbon cell structure operate in a differential cascode structure. A differential cascode structure has been used due to CMOS process issues. The transistor used was NMOS, and the size of each transistor is in Table 2. Additionally, a ribbon cell structure was proposed to improve the linearity of the power amplifier.

## A. Differential Cascode structure

The CMOS process is grounded with a bonding wire or metal line. Because there is no ground VIA. Therefore a differential amplifier structure was used to provide a virtual

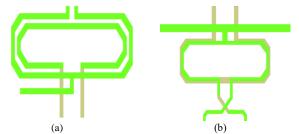

Fig. 1. Transmission line transformer matching network

(a) Input TLT design (b) Output TLT design

TABLE I. Transmission Line Transformer Parameters.

|                             | Input TLT     | Output TLT            |

|-----------------------------|---------------|-----------------------|

| Туре                        | Edge Coupling | Broadside<br>Coupling |

| Primary<br>(Metal /Width)   | OI / 5um      | OI / 5um              |

| Secondary<br>(Metal /Width) | IB/8um        | IB/ 5um               |

| Size                        | 170um x 135um | 160um x 155um         |

a. Corresponding author; gh.jeong@hanbat.ac.kr

Fig. 2. Schematic of the proposed CMOS Power Amplifier

| TR<br>Name | Gate finger<br>width | Number of fingers | Multiplier | Total<br>Gate width | Gate<br>length |

|------------|----------------------|-------------------|------------|---------------------|----------------|

| M1~M4      | 2 um                 | 16                | 8          | 256 um              | 0.03 um        |

ground. And when a differential amplifier structure is used, conversion between RF and differential signals is required. Therefore, a transmission line transformer (TLT) was used at the input and output to operate as a balun. In addition, the TLT allows the input and output impedance of the power amplifier to be matched. The input and output TLTs are shown in Figure 1 and the parameters are shown in Table 1. The input TLT is an edge coupling type with a size of 160um x 155um and the output TLT is a broadside coupling type with a size of 170um x 135um.

In addition, the proposed power amplifier has a cascode structure. This is because the CMOS process has a low breakdown voltage. The cascode structure provides sufficient voltage to the power amplifier. In addition, the cascode structure can reduce the Miller effect.

## B. Interstage inductor through Ribbon Cell structure

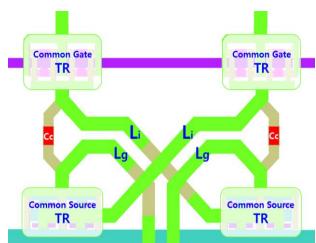

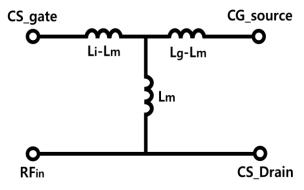

As the operating frequency increases, the real and imaginary parts of the drain impedance of a power amplifier using a cascode structure decrease due to parallel parasitic capacitance. However, if you connect a series interstage inductor between the Common Source (CS) amplifier and the Common Gate (CG) amplifier, The impedance of the real and imaginary parts of the drain increases.[6],[7] Therefore, mismatch of the power amplifier can be avoided through the series interstage inductor. However, mismatch can be avoided by inserting and connecting a large series inductor, but since the metal length increases to use a large inductance in the layout, the chip size increases and RF path loss occurs. To address the above problems, we propose a power amplifier using a ribbon cell structure. Figure 3 shows the layout of the proposed ribbon cell structure. The series interstage inductor  $L_i$ , which connects the drain of the CS amplifier and the source of the CG amplifier, is close to the gate metal line of the CS amplifier. In this layout, there is mutual indu-tance between  $L_i$  and  $L_g$ . Figure 4 is equivalently converted to the ribbon cell Structure T - model. It can be expressed as (1).  $L_m$  is the mutual inductance. Through the above equation, it can be confirmed

Fig. 3. Layout of the proposed Ribbon Cell

Fig. 4. T-model of Ribbon Cell

TABLE 3. Mutual Inductance of Ribbon Cell

| L     | 41.5 |   |

|-------|------|---|

|       |      |   |

| $L_i$ | 47.3 |   |

| $L_g$ | 55   |   |

| m     | 18   | _ |

that there is mutual inductance, and the inductance of Li appears larger due to the mutual inductance. Therefore, the desired value of inductance can be achieved by using a small inductor, resulting in a size advantage. Table 3 shows the mutual inductance used in the proposed power amplifier.

#### III. SIMULATION RESULTS

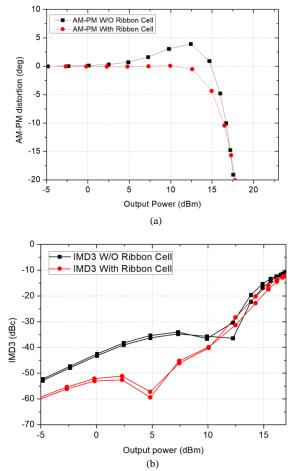

Linearity is improved when a ribbon cell structure is used in a CMOS power amplifier. Figure 5 and Table 4 show the AM-PM distortion and IMD3 simulation results with and without the ribbon cell structure. With the ribbon cell structure, an IMD3 of -40dBc is achieved at 10 dBm output power, and an IMD3 of -30dBc is achieved at 12.3 dBm output power.

Fig. 5. Simulation results (a)AM-PM (b)IMD3

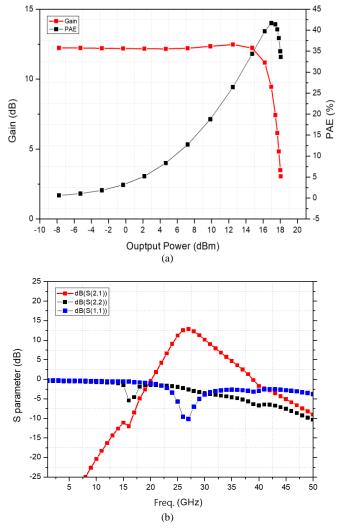

In Figure 6, it has a PAE of 19% and 25%. Therefore, with the ribbon cell structure, the desired series inductance can be used without increasing the size of the layout due to the inductor, and linearity is improved.

TABLE 4. Simulation Results of Linearity With ribbon cell W/O ribbon cell3 result result 3.8 at 12dBm -0.38 at 12dBm AM-PM 3.1 at 10dBm 0.08 at 10dBm -30dBc at 12.3 -40dBc at 10 dBm IMD3 -30dBc at 12.1 dBm dBm Linear PAE 19% (IMD3 -40dBc)

Fig. 6. Simulation results (a)Gain, PAE (b)S-parameter

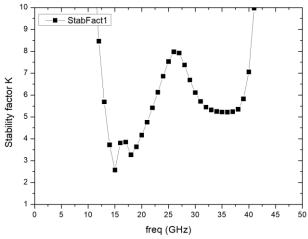

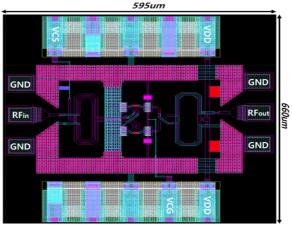

Figure 6 shows the 1-tone simulation results of a CMOS power amplifier with a ribbon cell structure. At a frequency of a 28 GHz, the gain is 11.6 dB and the peak PAE is 41.8%. The S-parameter results, S(1,1) / S(2,2) / S(2,1), are -7 dB / -3 dB / 12.4 dB at 28 GHz frequency. The results in Figure 7 show that the stability factor is greater than 1 at all frequencies, indicating unconditional stability. Figure 8 shows the layout of the proposed CMOS power amplifier. It

has a size of 595um x 660um including the ESD PAD. Table 5 shows the performance comparison with a 28GHz CMOS PA with linearization.

Fig. 7. Stability factor

Fig. 8. Proposed CMOS Power Amplifier layout

TABLE 5. Performance Comparison with 28GHz CMOS PA with Linearization

|                         | [8]         | [9]                      | This Work<br>(Simulated) |

|-------------------------|-------------|--------------------------|--------------------------|

| Freq (GHz)              | 28          | 28                       | 28                       |

| Linear Power (dBm)      | 11          | 7.5                      | 12.3                     |

| Peak PAE(%)             | 43.3        | 27.3                     | 41.8                     |

| Gain (dB)               | 13.6        | 18                       | 12.4                     |

| # of stage              | 1           | 2                        | 1                        |

| Linearization           | 2fo control | Dual power<br>mode S-PCC | Ribbon cell              |

| Area*(mm <sup>2</sup> ) | 0.78        | 0.5                      | 0.4                      |

| Process                 | CMOS 28nm   | CMOS 65nm                | CMOS 28nm                |

<sup>\*</sup>including pads

## IV. CONCLUSION

This paper proposes a ribbon cell structure to improve the linearity of a CMOS power amplifier operating at 28 GHz. As a result of the simulation, the AM-PM is 0.08 degrees at 10dBm and -0.38 degrees at 12 dBm. The IMD3 results are

-40 dBc at 10 dBm and -30 dBc at 12.3 dBm, with PAEs of 19% and 25%, respectively. It has a gain of 11.6 dB, a peak PAE of 41.8%, and a stability factor of more than 1, so it is unconditionally stable.

#### ACKNOWLEDGMENT

The chip fabrication and EDA tool were supported by the IC Design Education Center (IDEC), Korea.

This work was supported by the National Research Foundation of Korea(NRF) grant funded by the Korea government(MSIT)(No. 2022R1G1A1003448)

#### REFERENCES

- [1] T. Joo, B. Koo, and S. Hong, "A WLAN RF CMOS PA with Large-Signal MGTR Method," *IEEE Transactions on Microwave Theory and Techniques*, vol. 61, no. 3, pp. 1272-1279, Mar. 2013.

- [2] S. Jang, C. Lee, and C. Park, "Differential 2.4-GHz CMOS Power Amplifier Using an Asymmetric Differential Inductor to Improve Linearity," *Journal of the Korean Institute of Information and Communication Engineering*, vol. 23, no. 6, pp. 726-732, Jun, 2019.

- [3] N. Ryu, B. Park, and Y. Jeong, "A fully integrated high efficiency RF power amplifier for WLAN application in 40 nm standard CMOS process," *IEEE Micowave* and Wireless Components Letters, vol. 25, no. 6, pp. 382-384, Jun. 2015.

- [4] H, Ahn et al., "A Fully Integrated Dual-Mode CMOS Power Amplifier With an Autotransformer-Based Parallel Combining Transformer," *IEEE Micowave and Wireless Components Letters*, vol. 27, no. 9, pp. 833-835, Sep. 2017.

- [5] T. Joo, B. Koo, and S. Hong, "A WLAN RF CMOS PA with adaptive power cells," in *Proc. IEEE RFIC Symp.*, Seattle, WA, USA, 2013, pp. 345-348.

- [6] Oh, Juntaek, Bonhyun Ku, and Songcheol Hong. "A 77-GHz CMOS power amplifier with a parallel power combiner based on transmission-line transform er." *IEEE Transactions on Microwave Theory and Techniques* 61.7 (2013): 2662-2669.

- [7] Park, Jinseok, Seunghoon Kang, and Songcheol Hong. "Design of a Ka-band cascode power amplifier linearized with cold-FET interstage matching network." *IEEE Transactions on Microwave Theory* and Techniques 69.2 (2020): 1429-1438.

- [8] B. Park et al., "Highly linear mm-wave CMOS power amplifier," IEEE Trans. *Microwave Theory and Techniques*, vol. 64, no. 12, pp. 4535–4544, Dec. 2016.

- [9] S, Lee Seunghoon Kang, and Songcheol Hong. "A 28-GHz CMOS linear power amplifier with low output phase variation over dual power modes." IEEE

Microwave and Wireless Components Letters 29.8 (2019): 551-553.

Younseok Han received the B.S degree in the department of information and communication engineering at Hannam University, Daejeon, South Korea, in 2024.

He is currently working toward the M.S degree in department of intelligent nano semiconductor engineering, Hanbat National

University, Daejeon, South Korea. His current research interests include CMOS Power Amplifier for Ka-band And GaAs Power Amplifier for X-band

**Seungchan Lee** received the B.S.,M.S., and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea,in 2015, 2017, and 2021, respectively.

He was a post-doctoral researcher at University of California Santa

Barbara, Santa Barbara, CA, USA from 2021 to 2023. He was involved in various ICs and phased-array module development projects for 6G communication using GlobalFoundries RF-SOI and Intel16 FinFET processes. He is currently an Assistant Professor with the Department of Electronics Engineering, Chonnam National University, Gwangju, South Korea. His current research interests include millimeter-wave and Sub-THz integrated circuits and systems, and phased array systems for future wireless communications. Dr. Lee was a recipient/co-recipient of Grand Prize in the 25th Human-Tech Paper Award hosted by Samsung Electronics in 2019, a Minister Award of the Ministry of Science and ICT of Korea in 2020, and a Prime Minister Award of the Republic of Korea in the Korea Semiconductor Design Competition in 2020.

**Dong-Ho Lee** received the B.S., M.S., and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology, Daejeon, South Korea, in 2000, 2002, and 2007, respectively.

From 2007 to 2009, he was with the Microwaves Applications Group,

Georgia Institute of Technology, Atlanta, GA, USA, where he developed complementary metal oxide semiconductor (CMOS) power amplifiers for mobile communications. In 2009, he joined Skyworks Solutions Inc., Cedar Rapids, IA, USA, where he was involved in the design of power amplifiers and front-end modules for cellular handsets. In 2010, he joined Hanbat National University, Daejeon, South Korea, as a faculty member. His research interests include RF power amplifiers, microwave modules, ultrasonic applications, and radar systems.

Jeong Professor Gwanghyeon Jeong received B.S. and M. S. and the Ph.D electrical degree in engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 2012, 2014, and 2018, respectively.

He was with the Agency for Defense Development (ADD) from May 2018 to January 2021, and Hannam University from March 2021 to February 2023. He is now with the department of semiconductor system engineering, Hanbat National University, Daejeon, South Korea, as an assistant professor from March 2024. His research interests are RF circuits and systems for future wireless communications.