# 128-Channel Recording, 32-Channel Stimulation, Digitally Interfaced Optogenetic Neuromodulation System-on-Chip

Sang Min Song<sup>1</sup>, Min Jae Kim, Joon Gyu Kim, Hyun Tae Park, Young Hoon Park, Kyung Sik Eom<sup>a</sup> and Sung Yun Park<sup>a</sup>

Department of Electronics Engineering, Pusan National University E-mail: ¹aak4545@pusan.ac.kr

Abstract - This paper presents a digitally interfaced a 128-channel recording, 32-channel stimulation optogenetic neuromodulation system on chip (SoC) that has been developed for long-term optogenetics neuroscience research. The low-power 128-channel neural recording frontend offers low-noise multichannel recording, on-chip 16-bit data digitization, and electrode impedance measurement. The 32-channel optogenetic stimulator provides high-resolution, accurate optical stimulation. The chip communicates through two control signal shared SPI interfaces for simultaneous recording and stimulation with independent on-the-fly control command and data transfer, resulting in only 6 external wires. The developed system constitutes a fully digital, bidirectional 128/32-channel SoC suitable for *in-vivo* neuromodulation.

Keywords—Application-specific integrated circuit (ASIC), Multichannel neural recording and stimulation, Neuromodulation, Optogenetics

## I. INTRODUCTION

Since the first introduction of optogenetic research in 2005 [1], it has been gaining its popularity in neuroscience community. This technique genetically modifies specific types of neurons to express light-sensitive ion channels, opsins, on their membranes. The light-sensitive channels thus, react to specific wavelength of light to excite or inhibit neural activities. Compared to traditional electrical current, voltage, or charge-based stimulation, the newly introduced optical stimulation is more cell-specific. It also makes simultaneous recording much easier, while the electrical method tends to saturate the recording amplifier or induces huge artifacts that cannot be easily compensated afterwards.

For a complete optogenetic system that enable recording and stimulation simultaneously, there are many design criteria need to be met. The interconnection between blocks, the heat dissipation, and the power and timing distribution are the first challenges to overcome [2], [3]. On top of that, as the application is focused on implantable devices, it becomes increasingly more complicated. Bio-compatible

a. Corresponding author; Kyungsik Eom (kseom@pusan.ac.kr) and Sung-Yun Park (sungyun@pusan.ac.kr)

Manuscript Received Dec. 30, 2021, Revised Mar. 17, 2022, Accepted Mar. 20, 2022

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<a href="http://creativecommons.org/licenses/bync/3.0">http://creativecommons.org/licenses/bync/3.0</a>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

material for the implanted devices is the first necessity to be considered for the safety and long-term recordings with animal-under-test. Temperature change also needs to be closely tracked to maintain a safe environment for the brain cells of the animal- under-test. The system weight is also important. The total system weight, including everything on the system, should be no more than 10% of the animal weight. When the test object is a larger animal, like a rat or a genuine pig, around a 30-gram constraint is applied. However, for smaller rodents like mice, a strict 2-gram system is required [4].

Frontend integrated circuit architectures for multichannel neural recordings to achieve performance for neural recordings while maintaining low-power and small-area consumptions have been extensively researched, each with a specific set of pros and cons [5]-[8]. The ac-coupled architecture may be one of the most widely adopted architectures [9], [10]. It solves the issue of large electrode dc offset (EDO) and provides balanced performance between noise, power, gain uniformity, distortion, and so on. However, the ac-coupled architectures require relatively large physical area to implement EDO rejection. This large area consumption issue in the ac-coupled architectures has been solved by the dc-coupled frontend. It optimizes the circuit area by eliminating the large input capacitor and adopting mixed-signal feedback loops for the EDO suppression, however, with limitations to linearity and noise performance. The dc-coupled direct ADC has come out most recently [11]. The  $\Delta$ -modulation [12], [13] and switched capacitor (SC)-based direct sampling [14], and the difference differential amplifier (DDA) input stage-based  $\Delta$ modulation can achieve a rail-to-rail input range, removing the EDO concern, but with the cost of a high oversampling rate (OSR), i.e., high power consumption, and thereby limiting their applications to very low frequency neural signals, such as electroencephalogram (EEG), intracranial EEG (iEEG), electrocorticogram (ECoG), and field potentials.

It is also important to select an implantable neural stimulator suitable for the given environment. There are many different electrodes available for neural stimulations, resulting in a vast range of potential electrode impedances according to types (e.g., surface or penetrating), geometry and size, and materials. Therefore, the desired stimulation strength can vary a lot, for instance, the electrical stimulation using dc current uses from a few µA for intracortical

1

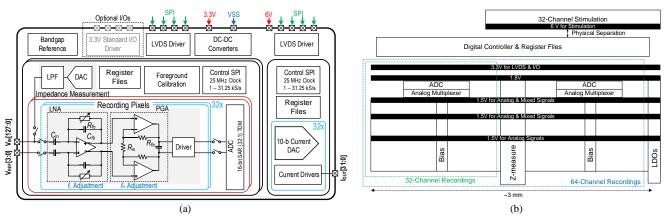

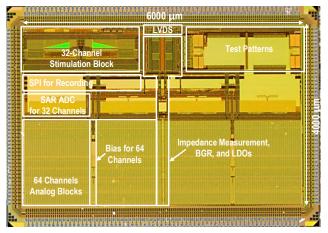

Fig. 1. Proposed 128/32-channel neuromodulation ASIC: (a) ASIC block diagram, (b) Simplified 64-channel floorplan for SoC implementation.

stimulation to a few mA for motor muscle and cortical stimulations, with variety of the requirement of precision, and waveform, and timing. In addition, not only for the electrical current stimulations, but also different stimulators have also been published, such as charge-controlled stimulation and voltage-controlled stimulation [15].

In this paper, a neuromodulation system on chip (SoC) with 128-channel recording and 32-channel optogenetic stimulation has been presented, which is designed for longterm optogenetics neuroscience research. This SoC provides a digitally interfaced, bidirectional, multi-parallel interface to neurons in the brain. This neuromodulation SoC relies on an external processing unit for the closed-loop operation. Even though it has inherently higher latency and power consumption for data transmission than the systems that have on-chip processing and control units, it has greater flexibility, as processing algorithms, such as feature extraction and classification can easily be reprogrammed and adjusted on-the-fly according to the testing environment. In addition, this external processing can relax power constraints on the classification hardware, allowing computationally extensive algorithm can be adopted for better accuracy.

The ASIC provides a 128-channel/32-channel interface to the brain for any processing entity capable of SPI command and data transfer and is therefore easy to employ. To cover many different application scenarios, the SoC is capable of low-noise neural recording in both local field potentials (LFPs) and action potentials (APs) frequency bands with bandwidth adjustments, as well as high-precision stimulation for  $\mu$ LEDs with ~50 dB of dynamic range (DR). A larger channel count can be easily accommodated by the modular, expandable design, which allows controlling several SoCs simultaneously.

Fig. 2. Block diagram of proposed system integration, including chip and base station side respectively.

### II. 128/32-CHANNEL NEUROMODULATION ASIC

Fig. 1(a) shows the proposed application specific integrated circuit (ASIC) architecture for 128-channel recording and 32-channel optogenetic stimulation SoC. The recording ASIC is 32-channel modular, consists of 4 modules to realize the total 128 channels. The stimulation ASIC is also 32-channel modular, only a single module has been implemented with the recording circuit. The SoC includes all necessary references, such as a bandgap reference (BGR), current references ( $\beta$ -multiplier), power rails (1.2, 1.5, and 1.8 V) from the internal low dropout regulators (LDOs), standard SPI I/O, and low voltage differential signaling (LVDS) drivers. Thus, only two supplies, 3.3 V and 6 V dedicated for recording and stimulation, respectively, are required. Fig 1 (b) shows the floor plan for the ASIC. Since the ASIC includes many different functionalities, the careful floorplan is necessary. The recording channel is assigned column-parallel, each occupies 40 µm pitch with 5 µm physical separation (thus, 45 µm pitch for each) and the staggered pads have been employed to accommodate the inputs with such a narrow pitch. As shown in Fig. 1 (b), the single module has its own bias block, 2 modules share a digital controller and a SPI, and 4 modules share the LDOs. For the stimulation ASIC, there is a dedicated SPI and LVDS driver but its control signals, such as CS\_b and SCLK, can be shared with the recording circuit. The power rails have been also planned to minimize the inference coupling. As shown, the analog supplies, such 1.2, 1.5 V and the digital supply 1.8 V are separately generated in the bottom and top size, respectively. The stimulation circuits that consume relatively higher peak power than recording circuits has been placed on top of the controller with > 100 µm physical separation.

## A. Analog Frontend Circuit for Neural Recording

In this work, the ac-coupled architecture has been implemented to inherit its advantages over the newly developed dc-coupled or direct-ADC architectures, such as excellent gain uniformity across the multiple channels, less design effort due to the well-developed design procedures, inherent passive offset cancellation, and relatively high input impedance, while compensating the high power and large area consumptions with the proposed novel circuit design

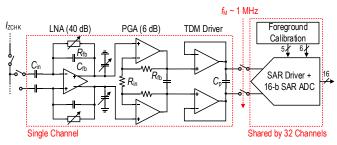

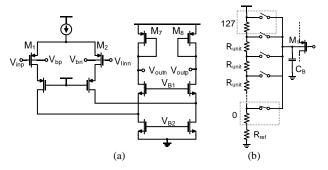

Fig. 3. (a) Implemented FC-OTA for the LNA where the source degeneration resistors have been replaced by the transistors and those transistors are re-used for the CMFB operation [16], and (b) the layout comparison with a conventional FC-OTA.

techniques. Fig. 2 shows the analog frontend circuit diagram for neural recordings. The frontend AC-coupled amplifier (LNA) provides a low noise and bandpass-shaped recording. The LNA can adjust the low cut-off frequency  $(f_L)$  from sub-Hz to a few Hz and the high cut-off frequency  $(f_{\rm H})$  from a few kHz with a fixed 40 dB mid-band gain. The  $f_L$  is adjusted via the pseudo resistor with a 2-b current digital to analog converter (DAC) and the  $f_{\rm H}$  is changed through the output capacitance  $(C_L)$  adjustment. The following programmable amplifier (PGA) has been implemented with non-inverting resistive feedback structure, therefore the combination of the LNA and the PGA looks like a conventional instrument amplifier with 3 amplifiers. The PGA also provides additional  $f_{\rm H}$  adjustment allowing the frontend circuit to be reconfigured to record low frequency neural signals. This can achieve 6 dB gain with high frequency cut-off adjustment from 1 kHz to 15.5 kHz. When considering the bandwidth, the recording channel has a capability to embrace LFPs and extracellular action potentials (APs) simultaneously, those are essential for the in-depth neuroscience research, and can be reconfigured to record ECoG while saving the power consumption. All recording channels have a time-division multiplexing (TDM) buffer to share the 16-b successive approximation register (SAR) ADC. The SAR ADC has been implemented using a split-capacitor array DAC, preamplifier, latched comparator, and control logics. The SAR ADC has two foreground calibration loops, each for the comparator offset and capacitor DAC calibrations.

The conventional circuit topologies have been adopted for the transistor-level implementations in non-critical circuit blocks. For instance, the class AB amplifiers were used for the PGA and driver implementation, and a conventional StrongArm latched comparator and split capacitor (6-10) DAC were employed for the SAR ADC. However, the most critical circuit block, LNA has been carefully realized with newly developed technique because it is one of the most power and area consuming blocks in the neural recording frontend. The implemented operational transconductance amplifier (OTA) for the LNA is shown in Fig. 3 (a), which is based on our previous implementation [16]. The backbone of the OTA is a folded-cascode OTA (FC OTA) that has been widely adopted for neural recording applications due to its favorable characteristics, such low-power and low-noise performance. However, the implementation of this OTA is bulky due to the resistor-based source degeneration and the necessary of the common mode feedback (CMFB) circuit for fully differential operation. In the implementation, the area-consuming resistors have been replaced the small transistors ( $M_{R1-4}$ ), and they are reused for the CMFB sensor. The CMFB servo loop has been realized by the folded cascode branch (M<sub>5-8</sub>), therefore the additional OTA for the CMFB has been completely removed. In addition, the output capacitor has been split as shown in Fig. 3 (a) to enhance the bandwidth of the common mode loop. Fig. 3 (b) shows the area comparison between the conventional FC-OTA and the implemented FC-OTA, indicating reduction of area and power ~37% and ~11%, respectively, while exhibiting the same noise performance.

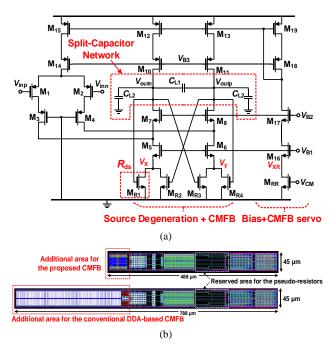

Fig. 4. Implemented 16-b split capacitor (6 + 10-b) capacitor DAC (CDAC) describing CDAC calibration procedures ((a) and (b))

## B. Circuit for 16-b SAR ADC with Foreground Calibration

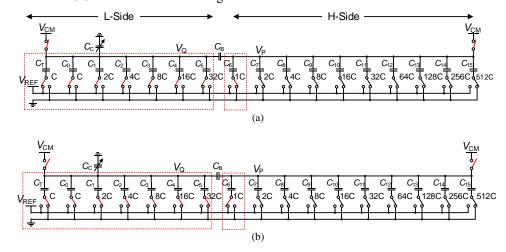

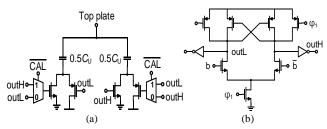

This work includes two 16-b split capacitor (6 + 10-b) SAR ADCs, each has two separate foreground calibrations. Figs. 4 (a) and (b) shows the capacitor DAC (CDAC) calibration. In the beginning of the calibration, all L-side capacitors are connected to  $V_{\text{REF}}$  (1111111), and all H-side capacitors are grounded (00000000). Since the calibration capacitor,  $C_{\rm C}$  is initially set to the lowest value in its tunable range, the total weight of the L-side is initially larger than that of the lowest bit in the H-side. Due to the charge conversation in the node  $V_{\rm P}$ ,  $V_{\rm P}$  becomes smaller than  $V_{\rm CM}$  after the all capacitors in the L-side are switched to the ground (0000000) and the lowest capacitor in the H-side is connected to  $V_{\rm REF}$ . The comparator compares  $V_P$  and  $V_{CM}$  and delivers the results to increase  $C_{\rm C}$  until  $V_{\rm P}$  becomes larger than  $V_{\rm CM}$ . Another calibration is for the comparator offset removal. Before the CDAC calibration, the top plates of the CDAC are set to  $V_{\rm CM}$ and the body biases of the input pair of the preamplifier shown in Fig. 5 (a) are swept using the resistor DAC (RDAC) shown in Fig. 5 (b). The ratio of the transconductance of the input pair,  $M_{1,2}$  ( $g_m$ ) to the body transconductance ( $g_{mb}$ ) is ~0.3<sup>-1</sup>, thus  $\Delta V_{BS} = 15$  mV is required to cover the offset of  $\pm 5$  mV.  $\Delta V_{BS}$  can be realized by the 7-b RDAC, resulting a LSB of ~117  $\mu$ V. The unit resistance (R<sub>unit</sub>) of ~6  $\Omega$  has been employed with the reference resistor (R<sub>REF</sub>) of  $\sim 77 \text{ k}\Omega$ . The large resistance distribution, such as 6  $\Omega$  to 77 k $\Omega$  has been laid out with a unit 60  $\Omega$  poly resistor with 10× parallel combinations and 10 segments of 128× series combination  $(10\times7.7~k\Omega).$  The static current consumption in the resistor string is  $\sim$ 19.3  $\mu$ A. For the energy-efficient operation of the SAR ADC, V<sub>CM</sub>-based switching scheme has been adopted [17]. To generate the necessary  $V_{CM}$  (= 1.5/2 V) without using amplifiers, the unit CDAC structure and the control circuit shown in Fig. 6 has been used [18]. To make the converter not to be limited by thermal noise, the total capacitance has been set as > 30 pF,  $(2kT/C < 27.6 \times 10^{-9} V^2)$ , i.e., 16.6  $\mu V_{rms}$ ) with the given 32.7  $\mu V_{rms}$  of the least significant bit (LSB). The unit capacitance ( $C_U$ ) has been set

Fig. 5. (a) Preamplifier for the latched comparator, (b) 7-b RDAC for the offset calibration

Fig. 6. Unit CDAC: (a), and the controller for the unit CDAC (b).

as 35.6 fF that thus, constitutes the total capacitance of 35.45 pF.

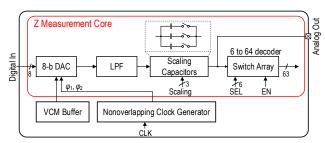

#### C. Circuit for Electrode Impedance Measurement

To improve system's functionality and safety, monitoring the electrode impedance is helpful. Tissue reactions over long-term recordings can significantly alter the electrodetissue interface, resulting in changes in electrode impedance, which can affect the recording quality. In addition, the impedance measurement before and after assembly would increase the recording yields. Therefore, tracking of the impedance allows monitoring the electrode condition and enhance the recording quality over time. In this work, the dedicated impedance measurement circuit has been implemented with the recording frontend circuit as shown in Fig. 7. The 8-b DAC receives a sinewave and converts it into a voltage waveform with a full scale of 1.2 V. After filtering, this voltage waveform is converted into a current through the selectable capacitors (0.1, 1, and 10 pF), then applied to the electrode under test. The impedance measurement procedures are controlled in the software where the appropriate scaling capacitor to prevent the saturation in the recording channel is selected and all 64 channels are swept sequentially. The amplified sinewayes are analyzed and the impedance information at a specific frequency (applied through the 8-b DAC) is extracted in the software. To cover all 128 channels in the system, two impedance measurement circuits have been implemented.

## D. Digital Control and LVDS drivers

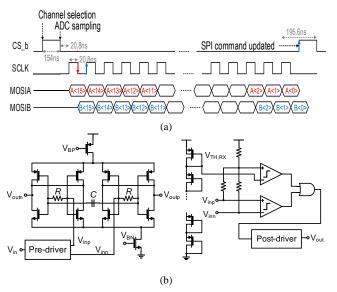

This neuromodulation ASIC has three dedicated SPIs, two for the 128-channel recording and one for 32-channel stimulation. Fig. 8 (a) shows a timing diagram for the SPI commands and data dedicated for recording. The single SPI period is 840.4 ns where 16 SCLKs are toggled with 40.8 ns period. In the digital controller, 5 commands are coded for the foreground calibration, chip reset, data conversion, and register read and write. The 32 SPI periods and 3 auxiliary SPI periods becomes 1 SPI cycle ( $35 \times 840.4$  ns), thus > 30kS/s sampling time is assigned for a single channel recording. The data conversion takes 3 SPI period to decode the conversion command (channel information), to covert the data, and to load the converted data into the SPI format. The 3 auxiliary SPI periods are also assigned for the register read and write, calibration, and chip reset. The single SPI dedicated for the recording basically operates for 32-channel, but it can cover 64 channels without increasing the clock rate by employing double data rate (DDR) technique as shown in

Fig. 7. Block diagram of proposed system integration, including chip and base station side respectively.

Fig. 8 (a). Fig. 8 (b) shows the core LVDS TX (left) and RX (right) drivers. For LVDS operation, a 3.3 V external supply is directly used. To filter out any glitches, a R-C low pass filter (LPF) has been implemented for the input of the TX driver. The threshold reference (V<sub>TH,RX</sub>) for the RX driver has been implemented using 6 PMOS stacks as shown in the right of Fig. 8 (b).

Fig. 8. Conceptual timing diagram for SPI operation (a), and core circuits for LVDS TX (left) and RX (right) drivers.

#### E. Optogenetic Stimulation

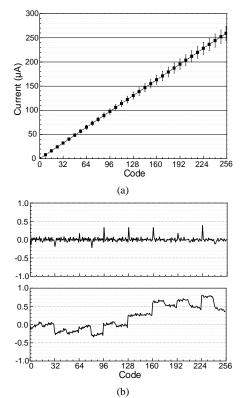

A previous version of the custom optogenetic stimulation ASIC to drive current to the  $\mu LEDs$  on the optoelectrode has been employed [19] with the resolution modification. The stimulation chip consists of 32 current DACs controlled by an SPI-based serial input. The DACs drive the  $\mu LEDs$  with up to 256  $\mu A$  current with 8-b resolution. The 1  $\mu A$  current steps provide fine control of emitted optical power while the large output range allows a high optical power option for neural activation in a large tissue volume. The output currents are simultaneously updated at the rate of 11.72 kHz by feeding 32 8-bit values into an input register which controls the output current level for each DAC channel.

Fig. 9. Die microphotograph for the fabricated neuromodulation ASIC

#### III. MEASUREMENT

The presented neuromodulation SoC has been fabricated with 180 nm 1P6M CMOS process. The die microphotograph is shown in Fig. 9 where the important circuit blocks are highlighted. The ASIC occupies  $6000 \times 4000 \ \mu m^2$  including test patterns. To accommodate 128 separate inputs and 4 reference inputs toward the single side of the chip (bottom), staggered pads have been employed.

## A. Benchtop Test

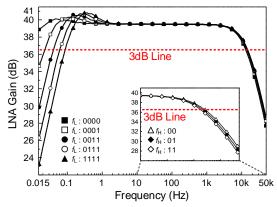

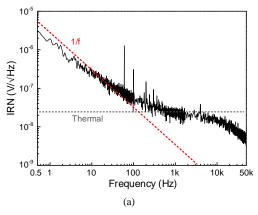

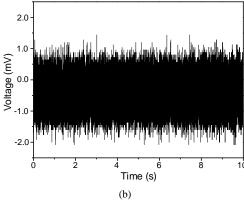

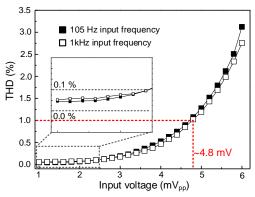

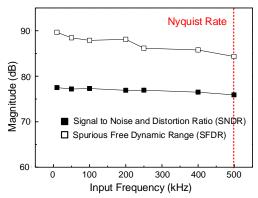

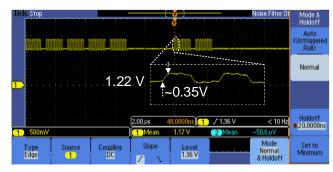

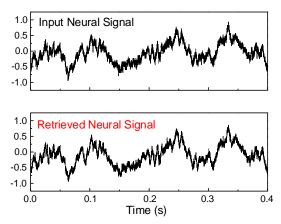

Fig. 10 shows the frequency response of the fabricated LNA using Agilent 35670A. The mid-band gain was ~39.5 dB. The measured bandwidth of the LNA spans from 0.0227 Hz to 14.642 kHz that can fully embrace LFPs and APs. As shown,  $f_L$  and  $f_H$  can be programmed from 22.7 to 87.3 mHz (2-b sets: 22.7, 39.8, 60, and 87.3 mHz) and from 12.541 to 14.642 kHz (1.5-b sets: 12.54, 13.55, and 14.64 kHz), respectively. Further  $f_H$  adjustment can be made when programming PGA (not shown) with 2-b; 8.0, 10.74, 12.16, 13.34 kHz. Fig. 11 (a) shows the input referred noise (IRN) spectrum of the LNA from 0.4 Hz to 50 kHz. The estimated 1/f noise corner was ~180 Hz and the power spectral thermal noise density was ~23 nV/ $\sqrt{\text{Hz}}$ . The calculated input referred noise (IRN) of the LNA was  $\sim$ 4.11  $\mu$ V<sub>rms</sub> from 0.4 to 10.5 kHz. Fig. 11 (b) depicts the transient output noise measurement of the same LNA using a Keysight MSO2004B for 10 seconds, that can cover down to 0.1 Hz. The calculated IRN from the transient measurement was ~4.24 µV<sub>rms</sub>, which is well matched to the spectral measurement in Fig. 11 (a). The measured total harmonic distortions (THDs) with 105 Hz and 1 kHz sinewaves are also shown in Fig. 12. The calculated THD from the measurement were  $\sim$ 1% for 4.8 mV $_{pp}$  inputs for both cases. Fig. 13 shows the measured signal to noise and distortion ratio (SNDR) and spurious free dynamic range (SFDR) up to the Nyquist rate (500 kS/s). The calculated effective number of bit (ENOB) was 12.31 bit at 499 kS/s. Fig. 14 shows the captured LVDS waveforms (MISO2) with a 100  $\Omega$  external resistor. The peak-to-peak amplitude was estimated as ~0.35 V with a 1.22 V common mode (CM) voltage while sending data to the host computer with 7m distance. The LVDS output can drive up 7 m of the flexible cable (RHD SPI cable, Intan Technology, USA) without bit errors. Fig. 15 shows the comparison between the pre-

Fig. 10. Measured frequency response of LNA

Fig. 11. Measurement noise characteristics: (a) spectral density of input referred noise, (b) transient output noise

Fig.12. Total harmonic distortion (THD) measurements for 105 Hz and 1 kHz sinewaves.

Fig. 13. SNDR and SFDR with various input frequencies.

recoded broadband neural signals (LFP + AP) and the output of the fabricated chip with the pre-recorded neural signals input. To fairly compare, the output has been referred to the input. Fig. 16 (a) and (b) show the dc-sweeping result of the optogenetic stimulator from code 0 to 255 and the calculated DNL (top) and INL (bottom), respectively. The max/min DNLs are 0.38/-0.2, thus there is no missing code. Table I summarizes the measurement results and compares with other state-of-the-art works. The presented work shows the highest level of integration by including all required circuit blocks on chip and has the largest number of parallel recording and stimulation.

TABLE I. Performance Comparison of Neural Interface

|                                  | a[2]                | [3]                 | This work           |

|----------------------------------|---------------------|---------------------|---------------------|

| Tech. [nm]                       | 180                 | 180                 | 180                 |

| Recording ASIC                   |                     |                     |                     |

| No. of Ch.                       | 32                  | 16                  | 128                 |

| Area/Ch. [mm <sup>2</sup> ]      | 0.46                | 0.1                 | 0.1312              |

| Power/Ch. [µW]                   | 11.8 (LNA)          | 9 (LNA)             | 13.2 (LNA)          |

| IRN [μVrms]                      | 3.8/3.3<br>(LFP/AP) | 4.57                | 4.1                 |

| ADC                              | Ι-ΔΣ                | V-ADC               | 16-b SAR            |

| Resolution (bit)                 | 16                  | 10                  | 16                  |

| ENOB                             | 12.1                | 9.1                 | 12.3 (worst)        |

| $f_{\rm L}\left({ m Hz} ight)$   | 0.2                 | 0.3                 | 0.02 - 250          |

| $f_{\rm H}\left({ m kHz}\right)$ | 7.5                 | 7                   | 7.6 - 13.4          |

| Sampling freq. (kS/s)            | 20                  | 1000/250<br>(CC/CV) | 31.25<br>(variable) |

| Supply Voltage (V)               | 1.8                 | 5                   | 3.3                 |

| Stimulation ASIC                 |                     |                     |                     |

| No. of Ch.                       | 32                  | 16                  | 32                  |

| Area/Ch. [mm <sup>2</sup> ]      | -                   | 0.013               | 0.09                |

| Power/Ch. [μW]                   | -                   | -                   | 975<br>@ 100 μA     |

| Resolution (bit)                 | -                   | 6                   | 8                   |

| Min. Current [μA]                | -                   | -                   | 1                   |

| Supply Voltage                   | ±9                  | 5                   | 6                   |

| Stimulation Type                 | Electrical          | Electrical          | Optical             |

| Others                           |                     |                     |                     |

| <sup>b</sup> PMU                 | N                   | N                   | Y                   |

| Z-Measurement                    | N                   | Y                   | Y                   |

<sup>&</sup>lt;sup>a</sup> Recording and Stimulation ASIC were integrated in one channel

<sup>b</sup> Power management unit

Fig. 14. Picture of the captured oscilloscope screen for LVDS measurement

### B. In Vitro Test

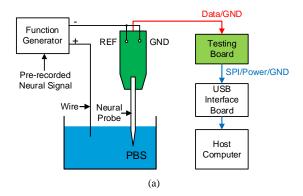

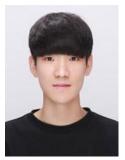

Before *in vivo* testing, the recording quality of the fabricated ASIC has been characterized *in vitro* setup. A custom silicon neural probe connected with the ASIC has been dipped in phosphate buffered saline (PBS) with the reference and ground connections. A set of pre-recorded

neural signals (recorded from motor cortex in a rat) then has been applied through PBS solutions. The schematic of the *in-vitro* testing setup is shown in Fig. 17 (a). The ASIC has been configured with the highest bandwidth to simultaneously record both LFP and AP signals and the recorded data has been collected using a customized USB-based interface board (XEM6010, OpalKelly, USA) and transferred to the host computer for further processing. The recorded raw data is shown in the top Fig. 17 (b). For better visualization, the raw neural signals have been bandpass filtered (3<sup>rd</sup>-order Butterworth,  $f_P = 0.8 - 7$  kHz,  $f_S < 0.6$ , > 8 kHz) using a commercial software (MATLAB, MathWorks, USA) and the resulting APs are shown in the bottom of Fig. 17 (b). An inset in Fig. 17 (b) depicts the enlarged ~80 ms of the LFP and AP.

Fig. 15. Prerecorded broadband neural signal (top) and the retrieved neural signal by this neuromodulation ASIC (bottom).

Fig. 16. DC-sweep from code 0 to 255 for the optogenetic stimulator (a), and DNL (top) and INL (bottom) (b).

Fig. 17. Schematic of the *in vitro* setup: (a) and retrieved raw data (top) and (b) filtered APs (bottom).

# IV. CONCLUSION

The of 128/32-channel on-chip integration a SoC neuromodulation for long-term optogenetic neuroscience research has been presented. The presented SoC consists of low-power, low-noise 128-channel neural recording frontends and high-precision 32-channel optogenetic µLED drivers. The recording frontends offer 128-channel simultaneous recording, on-chip digitization with 16-b resolution, and on-the-fly electrode impedance measurement, and the optogenetic drivers provides 32-channel simultaneous 8-b driving current with 1 µA resolution. The neuromodulation SoC communicates with a host computer using two SPI interfaces for recording and stimulation. Since the control signals for the SPIs can be shared, only 6 pins are required for the operation.

## ACKNOWLEDGMENT

The chip fabrication was supported by the IC Design Education Center (IDEC), Korea. The authors also would like to thank IDEC for the EDA software support. This work was also supported by National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) (2020R1A2C2101875) and by BK21PLUS, Creative Human Resource Education and Research Programs for ICT Convergence in the 4<sup>th</sup> Industrial Revolution.

#### REFERENCES

- [1] E. S. Boyden, F. Zhang, E. Bamberg, G. Nagel, and K. Deisseroth, "Millisecond-timescale, genetically targeted optical control of neural activity," *Nat. Neurosci.*, vol. 8, no. 9, pp. 1263–1268, 2005, DOI: 10.1038/nn1525

- [2] S. Reich, M. Sporer, M. Haas, J. Becker, M. Schuttler, and M. Ortmanns, "A High-Voltage Compliance, 32-Channel Digitally Interfaced Neuromodulation System on Chip," *IEEE J. Solid-State Circuits*, pp. 1–1, 2021, DOI: 10.1109/jssc.2021.3076510.

- [3] X. Liu, M. Zhang, A. G. Richardson, T. H. Lucas, and J. Van Der Spiegel, "Design of a Closed-Loop, Bidirectional Brain Machine Interface System with Energy Efficient Neural Feature Extraction and PID Control," *IEEE Trans. Biomed. Circuits Syst.*, vol. 11, no. 4, pp. 729–742, 2017, DOI: 10.1109/TBCAS.2016.2622738.

- [4] G. Buzsáki *et al.*, "Tools for Probing Local Circuits: High-Density Silicon Probes Combined with Optogenetics," *Neuron*, vol. 86, no. 1, pp. 92–105, 2015, DOI: 10.1016/j.neuron.2015.01.028.

- [5] W. Liew, X. Zou, and Y. Lian, "A 0.5-V 1.13μW/Channel Neural Recording Interface with Digital Multiplexing Scheme," in *European Solid State Circuits Conference*, 2011, pp. 219–222.

- [6] D. Yeager et al., "A 4.78mm2 Fully-Integrated Neuromodulation SoC Combining 64 Acquisition Channels with Digital Compression and Simultaneous Dual Stimulation," in *IEEE Symposium on VLSI Circuits*, Jun. 2014, pp. 1–2, DOI: 10.1109/VLSIC.2014.6858430.

- [7] B. C. Raducanu *et al.*, "Time Multiplexed Active Neural Probe with 1356 Parallel Recording Sites," *Sensors*, vol. 17, no. 10, p. 2388, 2017, DOI: 10.3390/s17102388.

- [8] S. Lee and J. E. Kim, "A 10-bit Single-Ended SAR ADC with Split Dual-Capacitive-Array for Multi-Channel Neural Recording System," *IDEC J. Integr. Circuits Syst.*, vol. 3, no. 1, pp. 1–6, 2017.

- [9] R. R. Harrison, "A Versatile Integrated Circuit for the Acquisition of Biopotentials," in *IEEE Custom Integrated Circuits Conference*, 2007, no. Cicc, pp. 115–122, DOI: 10.1109/CICC.2007.4405694.

- [10] R. R. Harrison and C. Charles, "A Low-Power Low-Noise CMOS Amplifier for Neural Recording Applications," *IEEE J. Solid State Circuits*, vol. 38, no. 6, pp. 958–965, 2003.

- [11] R. Muller, S. Gambini, and J. M. Rabaey, "A 0.013 mm2, 5 μW, DC-Coupled Neural Signal Acquisition IC with 0.5 V Supply," *IEEE J. Solid-State Circuits*, vol. 47, no. 1, pp. 1–12, 2012, DOI: 10.1109/JSSC.2011.2163552.

- [12] S.-Y. Park, J. Cho, K. Na, and E. Yoon, "Modular 128-Channel Δ-ΔΣ Analog Front-End Architecture Using Spectrum Equalization Scheme for 1024-Channel 3-D Neural Recording Microsystems," *IEEE J. Solid-State Circuits*, vol. 53, no. 2, pp. 501–514, 2018, DOI: 10.1109/JSSC.2017.2764053.

- [13] S.-Y. Park, J. Cho, K. Lee, and E. Yoon, "Dynamic

- Power Reduction in Scalable Neural Recording Interface Using Spatiotemporal Correlation and Temporal Sparsity of Neural Signals," *IEEE J. Solid-State Circuits*, vol. 53, no. 4, pp. 1102–1114, 2018, DOI: 10.1109/JSSC.2017.2787749.

- [14] H. Kassiri *et al.*, "Rail-to-Rail-Input Dual-Radio 64-Channel Closed-Loop Neurostimulator," *IEEE J. Solid-State Circuits*, vol. 52, no. 11, pp. 2793–2810, 2017.

- [15] J. Simpson and M. Ghovanloo, "An Experimental Study of Voltage, Current, and Charge Controlled Stimulation Front-End Circuitry," in *IEEE International Symposium of Circuits and Systems*, 2007, pp. 325–328.

- [16] J. Y. Kwak and S.-Y. Park, "Compact Continuous Time Common-Mode Feedback Circuit for Low-Power, Area-Constrained Neural Recording Amplifiers," *Electronics*, vol. 10, no. 2, pp. 1–11, 2021, DOI: 10.3390/electronics10020145.

- [17] Z. Zhu, Y. Xiao, and X. Song, "VCM-based monotonic capacitor switching scheme for SAR ADC," *Electron. Lett.*, vol. 49, no. 5, pp. 327–329, 2013, DOI: 10.1049/el.2012.3332.

- [18] C. Kao, S. Hsieh, and C. Hsieh, "A 0.5V 12-bit SAR ADC using Adaptive Time- Domain Comparator with Noise Optimization," in *IEEE Asian Solid-State Circuits Conference*, 2017, vol. 1, no. 2133, pp. 213–216.

- [19] A. E. Mendrela, K. Kim, D. English, S. Mckenzie, and J. P. Seymour, "A High-Resolution Opto-Electrophysiology System with a Miniature Integrated Headstage," *IEEE Trans. Biomed. Circuits Syst.*, vol. 12, no. 5, pp. 1065–1075, 2018, DOI: 10.1109/TBCAS.2018.2852267.

Sang Min Song received his B.S. in Electronic Engineering from Pusan National University, Busan, Korea in 2021, where he is currently working toward the M.S. degree in electrical and electronics engineering. His current research interests are in low-power, lownoise, high power conversion efficiency DC-DC converters and

photodiode with MPPT controller.

Min Jae Kim received his B.S. in Electronic Engineering from Pusan National University, Busan, Korea in 2021. His current research interests are in low-power, low-noise OTA for neural signal recording.

designs.

Joon Gyu Kim received his B.S. in Electronic Engineering from Pusan National University, Busan, Korea in 2021, where he is currently working toward the M.S. degree in electrical and electronics engineering. His current research interests are Two-Step SAR ADC Architecture using Time-Domain Comparator for low power and high resolution in CMOS

Hyun Tae Park received his B.S. in Electronic Engineering from Pusan National University, Busan, Korea in 2021, where he is currently working toward the M.S. degree in electrical and electronics engineering. His current research interests include time-domain VCO based Zoom ADC and incremental delta-sigma ADCs for low power

and high resolution in CMOS designs.

Young Hoon Park received B.S. degree in Electronics Engineering from Pukyong National University (PKNU), Busan, S. Korea, in 2020. His current research interests include the development of neural prostheses, especially retinal prostheses, and the development of safe and effective neural interfaces.

**Kyung Sik Eom** received B.S. degree in Electrical and Electronics Engineering from Korea Advanced Research Institute (KAIST), Daejeon, S. Korea, in 2010, the M.S. and Ph.D. degree in Electrical and Computer Engineering from Seoul National University, Seoul, S. Korea, in 2012 and 2016, respectively. From 2016 to 2019, he was involved

in developing a novel photonic retinal prosthesis using plasmonic nanoparticles as a post-doctoral research associate in the Department of Engineering at Brown University, RI, USA. In 2019, he joined the Department of Electronics Engineering at Pusan National University, Pusan, S. Korea, as an assistant professor. His current research interests include developing neural prosthesis especially the retinal prosthesis, developing safe and effective neural interface, and optical imaging tools for ophthalmology.

Sung-Yun Park received the B.S. degree in electrical engineering from Pusan National University, Busan, Korea, in 2005, the M.S. degree in electrical engineering from the Korean Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2008, and the M.Eng. degree in electrical and computer engineering and the

Ph.D. degree in electrical engineering from the University of Michigan in 2011 and 2016, respectively. He was involved in photonics device research with the Korean Advanced Institute of Science and Technology. From 2008 to 2010, he was a Member of the Technical Staff with Fairchild Semiconductor, Bucheon, Korea, for high voltage mixed signal circuit design. He continued his study in integrated circuits with Cornell University, Ithaca, NY, USA. From 2016 to 2018, he was a Research Fellow with the University of Michigan, where he has been an Assistant Research Scientist since 2018. In 2019, he joined the Department of Electronics Engineering, Pusan National University, where he is an Assistant Professor. His current research interests are low power, low noise mixed-signal integrated circuits and power management circuits for biomedical and sensor systems.