# Design Methodology for Capacitively Coupled Continuous-time Delta-sigma Modulator

Chae Gang Lim<sup>1</sup> and Chul Woo Kim<sup>a</sup>

Department of Electrical Engineering, Korea University E-mail : <sup>1</sup>lcg@kilby.korea.ac.kr

Abstract – This paper presents a design methodology for highlinearity capacitively coupled (CC) continuous-time deltasigma modulator (CTDSM). The third-order loop filter enables sufficient noise-shaping with a low oversampling ratio (OSR). The chip is implemented in a 180-nm CMOS process with an active area of 1.65 mm<sup>2</sup>, drawing 232.2 uA at a 1.8 V supply. The proposed CC-CTDSM has a 19.4 nV/ $\sqrt{\text{Hz}}$  input-referred noise density, 1.9 uV offset, 0.08% gain error, 16 ppm integral nonlinearity (INL), and 140 dB common-mode rejection ratio (CMRR) within an input range of 60 mV<sub>pp</sub>.

With -110.1 dB total harmonic distortion (THD), excellent dynamic linearity performance is achieved owing to the CCIAintegrated design and chopping artifact rejection technique.

*Keywords*—CCIA, Chopping, Continuous-time Deltasigma Modulator (CTDSM), High-linearity

### I. INTRODUCTION

A sensor readout IC is a fundamental circuit block used in instrumentation, bio-medical, and automotive applications. Consumer electronic sensors such as temperature, humidity, and acceleration sensors output electrical signals close to a DC with an amplitude of tens of millivolts. Readout ICs should have low noise, low offset, a high common-mode rejection ratio (CMRR), and high input impedance. In addition, the output of piezoresistive accelerometers, used in car crash and tactical weapon testing, and bio-potential such electrocardiogram signals as (ECG) and electroencephalogram (EEG) are AC responses. Owing to the increasing diversity in sensor applications, the demand for high dynamic linearity performance has increased.

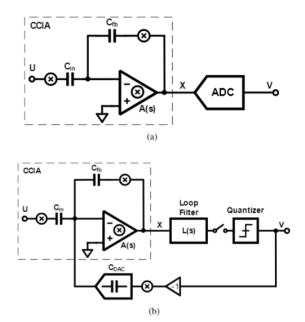

As shown in Fig. 1, a CCIA is a capacitive gain amplifier that adopts chopping as a dynamic offset cancellation technique, thereby achieving low noise and low offset. The CCIA is suitable for measuring DC signals because the gain is determined by the ratio of  $C_{fb}$  and  $C_{in}$ , which is insensitive to mismatch and exhibits high gain accuracy. However, when measuring AC signals, spikes caused by chopper

Fig. 1. (a) sensor ROIC with a CCIA, (b) capacitively coupled CTDSM.

switching and the nonlinearity of the CCIA limit the dynamic linearity of the entire system. In [1], a THD of -76 dB was achieved at an input range of 80 mV<sub>pp</sub>. Achieving higher dynamic linearity using CCIA necessitates a considerably larger quiescent current than that consumed by noise requirement. This is inefficient in terms of noise-dominated designs. Consequently, a sensor ROIC with high dynamic linearity (THD < -100 dB) using the CCIA has not been reported thus far.

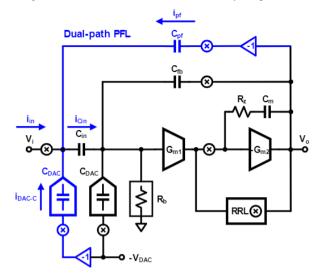

In this paper, we present a CC-CTDSM, as shown in Fig. 5. The CTDSM embeds the CCIA at the front-end to desensitize the nonlinearity of the CCIA. This architecture facilitates a highly linear sensor ROIC. As the CCIA is incorporated in the modulator, the CCIA only deals with the shaped quantization noise as the in-band STF is unity. The effective signal range is shrunk and the op-amp lies in a more linear swing range. Because it hardly provides a signal-dependent error, it can significantly increase the ROIC linearity. However, the CCIA chopper causes problems in the proposed CC-CTDSM.

The chopping artifacts generated in the CCIA are rejected with sampling frequency chopping and optimized RRL, and

a. Corresponding author; ckim@kilby.korea.ac.kr

Manuscript Received Oct. 20, 2021, Revised Dec. 01, 2021, Accepted Dec. 06, 2021

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<u>http://creativecommons.org/licenses/bync/3.0</u>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

chopping-induced in-band noise increase, distortion, and loop instability are avoided. Due to this feature, the proposed CC-CTDSM can employ the non-return-to-zero (NRZ) digital-to-analog converter (DAC) as the main feedback DAC of the modulator, which has alleviated amplifier speed requirement and better stability than the return-to-zero (RZ) DAC. Furthermore, no extra analog filters are located before or inside the ROIC owing to the inherent anti-aliasing characteristic of the CTDSM. This ROIC enables accurate sensing of AC signals since the internal chopping spikes are totally suppressed and the harmonic distortions of the CCIA are desensitized in the modulator loop.

The prototype chip is implemented in a 180-nm CMOS technology. It achieves 19.4 nV/ $\sqrt{\text{Hz}}$ , -110.3 dB THD, 1.9  $\mu$ V input-referred offset, 0.1% gain error, and 16 ppm INL over an input range of 60 mV<sub>pp</sub>.

# II. DESIGN CONSIDERATIONS FOR CC-CTDSM

## A. System Design

The chopping frequency of the proposed CC-CTDSM is equal to the sampling frequency. This condition forces a significantly higher chopping frequency to achieve sufficient quantization noise shaping. It enables to build a high-order loop filter with a 5-bit quantizer. Hence, this is possible to get a sufficient SQNR with a low OSR. In this article, a  $3^{rd}$ order loop filter is used with an OSR of 40. The signal bandwidth is 1 kHz, and the maximum out-of-band gain of the NTF is 2.5.

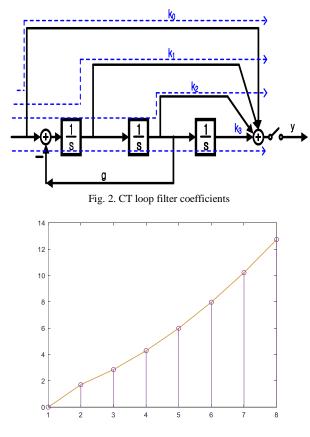

Fig. 3. Impulse response of the DT loop filter and CT converted one

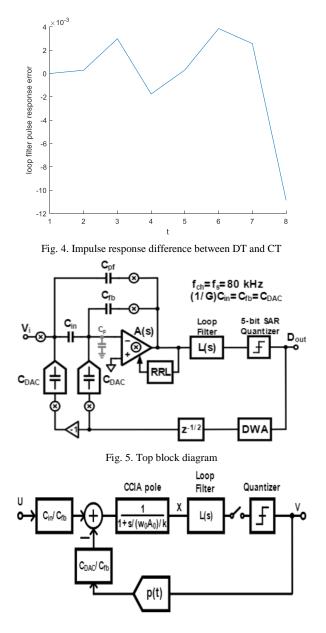

In order to build a noise transfer function (NTF) of the system, we used the Delta-Sigma toolbox to synthesize the NTF. The excess loop delay is assigned by 0.5*Ts* for the quantizer and DAC process time. The NTF is synthesized in discrete-time transfer function and converted into continuous-time format through impulse response matching as shown in Fig. 2. We can take into account the non-idealities of the amplifiers used in integrators. In the case of the first integrators, the amplifier parameters are extracted from CADENCE simulations. The two-stage miller-compensated amplifier gain is 130 dB and the bandwidth is 6 time of the sampling frequency. The impulse response of the DT and CT loop filters are shown in Fig. 3 and their difference is presented in Fig. 4.

In Fig. 5, the gain of the CCIA, G (=  $C_{in}/C_{fb}$ ) is fixed to 50 to amplify the millivolts range of the transducer output for the following ADC. As the CCIA itself is a closed-loop

Fig. 6. Linear model of the proposed CC-CTDSM with a CCIA pole

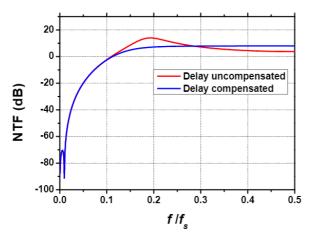

system, the finite bandwidth effect is simplified by generalizing CCIA as a one-pole system. Assuming that the op-amp has one pole, the CCIA provides an extra delay in front of the loop filter. The linear model of CC-CTDSM, including finite bandwidth of CCIA, is presented in Fig. 6. It is desirable that the CCIA bandwidth be sufficiently high to disregard the excess loop delay. In this design, the dominant pole of CCIA is near the sampling frequency,  $f_s$ . The delay is  $1/(2\pi f_s) \approx 0.16$ Ts in the first-order approximation. This delay can be compensated by an excess loop delay compensation circuit, as shown in Fig. 7.

# B. CCIA design

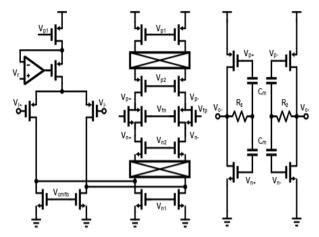

Fig. 8 shows a circuit diagram of the CCIA. A two-stage miller compensated op-amp is implemented with the RRL. The CM bias resistor is implemented using subthreshold biased transistors [2]. Both NMOS and PMOS transistors are used to provide a fast CM settling time. The resistance exceeds 50 M $\Omega$  in the steady state at half VDD bias, which has negligible noise contribution.

Fig. 9 shows a schematic of the two-stage op-amp. The op-amp input stage is a folded-cascode OTA with PMOS input transistors. The tail current source of the input stage is boosted for a higher CMRR. The source transistors of the

Fig. 7. NTF of CC-CTDSM with CCIA with delay compensation

Fig. 8. Front-end of CC-CTDSM (impedance boosting loop, bias resistor, two-stage op-amp, and RRL)

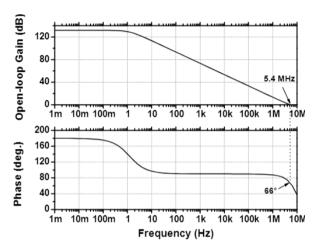

cascode stage are biased in strong inversion to reduce their thermal noise. The output choppers of the op-amp are placed between the current sources to avoid reduction in the op-amp gain due to parasitic capacitors. The first-stage transconductance  $G_{ml}$  is 342 µS. The DC gain of the op-amp is 130 dB, the unity-gain frequency is 5.4 MHz, and the phase margin is 66° as presented in Fig. 10.

Fig. 9. Schematic of two-stage op-amp used for CCIA

Fig. 10. Simulation results of the open-loop gain and phase of the opamp.

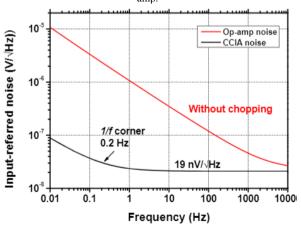

Fig. 11. Input-referred noise density of the op-amp and chopped CCIA.

The input-referred noise of the proposed system is dominated by  $G_{ml}$ . The  $G_{m2}$  noise and the following loop filter noise are attenuated by the open-loop gain of  $G_{ml}$  and closed-loop gain of the CCIA, respectively. As shown in Fig. 11, the CCIA input-referred noise is 19 nV/ $\sqrt{Hz}$  and the l/f corner is 0.2 Hz. The l/f noise is sufficiently attenuated by a chopping frequency of 80 kHz. The closed-loop pole of the CCIA is 80 kHz, which does not influence the transfer function of the following integrators.

The compensation transconductance  $G_{m3}$  and sensing capacitor  $C_s$  in the RRL determine the conversion gain, which involves noise-folding. For minimizing noise-folding,  $G_{m3}$  and  $C_s$  is set to 4.8 µS and 100 fF, respectively. In addition,  $A_{int}$  is a folded-cascode OTA with a 90-dB DC gain to achieve a steep loop gain of the RRL.

# C. CTDSM design

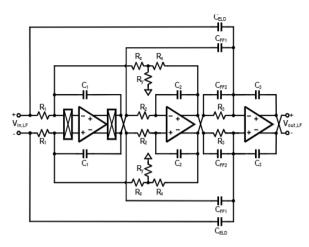

Fig. 12 shows the loop filter used in the CC-CTDSM. A third-order loop filter with an optimized NTF zero is implemented for energy-efficient quantizing compared to the low-order design. The CCIA structure is utilized to avoid an extra feedback DAC. Capacitor  $C_{FF1}$  and  $C_{FF2}$  provide a feedforward gain. The first integrator is chopped because the preceding capacitive gain stage does not completely suppress the 1/f noise of the integrator. To avoid chopping aliasing, the chopping frequency of the integrator is also

Fig. 12. Loop filter of the CC-CTDSM

Fig. 13. RC calibration circuit.

equal to the sampling frequency. For optimized NTF zero, the resonator resistor should be 675 M $\Omega$ , which is excessively bulky. Instead, the T-network comprises Rx, Ry, and R<sub>z</sub>, which form an equivalently large resistance of R<sub>z</sub>(R<sub>x</sub>/R<sub>y</sub>) [3]. The input resistor, R<sub>1</sub>, dominates the loop filter noise because the first integrator attenuates the noise in the following stages. However, driving an excessively small R1 is a burden on CCIA. Therefore, R<sub>1</sub> of 500k $\Omega$  is used in this design. Besides, R<sub>2</sub> and R<sub>3</sub> are 25 and 50 M $\Omega$ , respectively, thereby lowering the op-amp output loads.

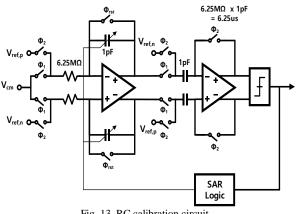

All capacitors in the loop filter have a 5-bit tuning range of 50% from nominal value to compensate the RC time constant variation. In addition, a dedicated RC calibration [4] circuit is implemented as shown in Fig. 13.

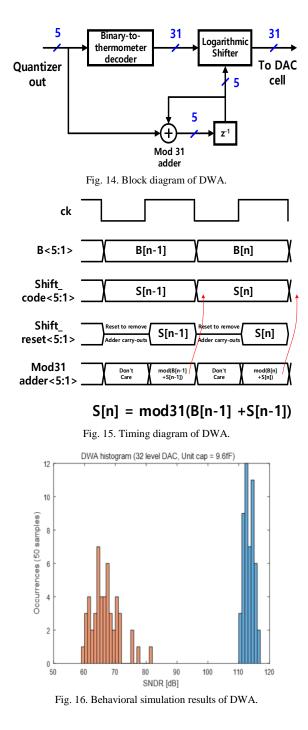

As the 5-bit quantizer and DWA logic contribute to the operation time, an excess loop delay should be assigned to secure modulator stability. Therefore, a half-cycle of the sampling frequency is assigned. An ELD compensation path is easily implemented because loop filter input contains a feedback DAC component. The C<sub>ELD</sub> and C<sub>3</sub> ratios comprise the compensation gain. The DWA logic is implemented as Fig. 14. Its timing diagram and operations are presented in Fig. 15. Through the behavioral simulations, the modulator can guarantee over 110 dB SNDR after the DWA as shown in Fig. 16.

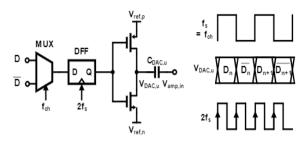

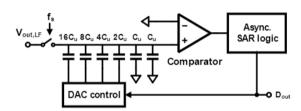

The SAR-type quantizer has the highest power efficiency under slow (80 kS/s) and low-resolution conditions (5-bit). Fig. 18 shows a single-ended diagram of the 5-bit SAR quantizer used in this design. The unit capacitor of the capacitive DAC of the SAR quantizer is 10 fF. Asynchronous SAR logic is implemented to avoid the use of an additional clock signal. The main feedback DAC of the CC-CTDSM is composed of a thermometer-based 31-unit CDAC cell, as shown in Fig. 17. The quantizer samples the loop filter output and digitizes it at the falling edge of  $f_s$ . After a half clock cycle, the DAC output  $V_{DAC,u}$  is updated

Fig. 17. Unit DAC cell of the CC-CTDSM and timing diagram.

Fig. 18. 5-bit SAR quantizer of the CC-CTDSM.

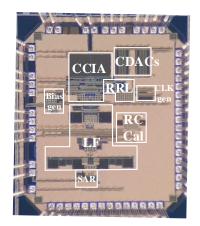

Fig. 19. Chip photograph.

at the rising edge of  $f_s$ . Because the DAC cell incorporates chopping, the update rate of the D flip-flop (DFF) is set as  $2f_s$  to generate the opposite data.

A prototype of the proposed CC-CTDSM is implemented using a 180-nm CMOS process. Fig. 19 presents a photograph of the fabricated chip, where the active are, including the RC calibration circuit, is 1.65 mm<sup>2</sup>. The chip consumes a current of 232.2 uA at a 1.8 V supply voltage.

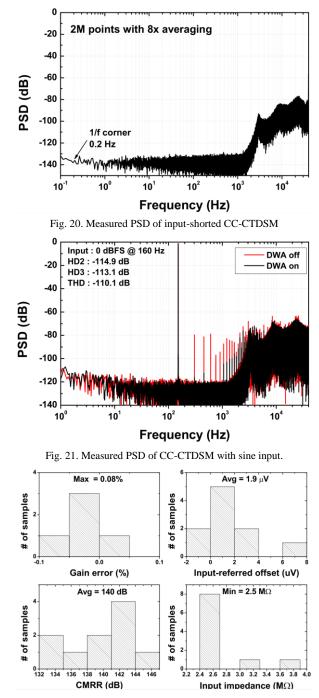

Fig. 20 shows measured PSD of the proposed CC-CTDSM with input shorting and Fig. 21 shows sine wave test for a dynamic linearity measurement. Fig. 22 shows measured DC performance of the ROIC. A performance summary and comparison with state-of-the-art sensor

Fig. 22. Measured gain error, offset, CMRR, and input impedance

|                                         | This work             | JSSC                     | JSSC                    | L-SSC                 | SOVC                  | SOVC                  | JSSC                   |

|-----------------------------------------|-----------------------|--------------------------|-------------------------|-----------------------|-----------------------|-----------------------|------------------------|

|                                         |                       | 2019 [5]                 | 2019 [6]                | 2019 [7]              | 2017 [8]              | 2018 [9]              | 2020 [10]              |

| Architecture                            | $CC-CT\Delta\Sigma M$ | CCIA+DT $\Delta\Sigma M$ | $CCIA+CT\Delta\Sigma M$ | $CC-CT\Delta\Sigma M$ | $CC-CT\Delta\Sigma M$ | $CC-CT\Delta\Sigma M$ | PLL- $\Delta \Sigma M$ |

| Technology (nm)                         | 180                   | 130                      | 180                     | 180                   | 40                    | 180                   | 40                     |

| Active Area (mm <sup>2</sup> )          | 1.65                  | 0.65                     | 0.73                    | 0.75                  | 0.06                  | 1.1                   | 0.025                  |

| Supply Voltage (V)                      | 1.8                   | 3(A) / 1.5(D)            | 1.8                     | 1.8                   | 1.2                   | 1                     | 0.8(A) / 0.6(D)        |

| Supply Current (µA)                     | 232.3                 | 326(A) / 20(D)           | 1200                    | 1200                  | 21                    | 6.5                   | 3.4(A) / 3.2(D)        |

| Bandwidth (kHz)                         | 1                     | 0.0025-0.04              | 2                       | 2                     | 2                     | 0.15                  | 10                     |

| Input Range (mVpp)                      | 60                    | 43.75 - 5600             | 20                      | 16                    | 100                   | 360                   | 100 / 400              |

| CM Input Range (V)                      | 0-1.8                 | 0–3                      | 0-3.3                   | 0-3.3                 | 0-1.2                 | 0-1.2                 | 0-0.8                  |

| Offset (µV)                             | 1.9                   | 1.87                     | 7                       | 300                   | _                     | _                     | 50                     |

| Input Noise Density<br>$(nV/\sqrt{Hz})$ | 19.4                  | 44                       | 3.7                     | 4.5                   | 140                   | 265                   | 36                     |

| CMRR (dB)                               | 140                   | 126                      | 134                     | 137                   | -                     | 84                    | 83                     |

| Gain Error (%)                          | 0.1                   | _                        | 0.3                     | 0.2                   | _                     | _                     | -                      |

| FoM* (dB)                               | 155.0                 | 169.3(@gain=1)           | 151.1                   | 148.6                 | 154.0                 | 160.9                 | 172                    |

| NEF / PEF                               | 11.2 / 224.8          | 6.6 / 130                | 5.0 / 45                | 6.1 / 67.0            | 22.6 / 612            | 26 / 676              | - / 8.9                |

| THD (dB)                                | -110.3                | _                        | _                       | _                     | -82                   | -104.7**              | -91**                  |

Table I. Comparison with State-of-the-art sensor readout ICs

\* FoM =  $10\log(V_{FS}^2/(8 \cdot v_n^2 \cdot P))$  \*\* SFDR \*\*\* PEF = NEF<sup>2</sup> ·  $V_{DD}$

readout ICs are depicted in Table 1. The left three readout ICs employ the CCIA front-end. These ICs are specialized in DC measurement systems such as a Wheatstone bridge sensor with low input-referred noise, offset, and high CMRR. In contrast, the right three paper are focused on AC measurements, such as Hall sensor or biopotential sensors with high dynamic linearity performance. However, they are not capable of AC measurement. The proposed sensor readout IC, however, is capable of both DC and AC measurement. It achieves 19.4 nV/ $\sqrt{Hz}$ , -110.3 dB THD, 1.9  $\mu$ V input-referred offset, 0.1% gain error, and 16 ppm INL over an input range of 60 mV<sub>pp</sub>.

# IV. CONCLUSION

This paper presents a high-dynamic-linearity CC-CTDSM for sensor readout applications. To obtain a high dynamic linearity, the CTDSM employs a CCIA as the front-end inside the loop; thus, the requirements of the op-amp are relaxed and CCIA processes only shaped quantization noise component and relax the input-dependent issues, i.e. input swing range and harmonic distortions. Using the chopping frequency as the sampling frequency enables us to ignore chopping aliasing and also reject chopping ripples and spikes. The third-order loop filter and 5-bit quantizer allow for a low chopping frequency. The DWA prevents a reduction in linearity by a static mismatch in the main feedback DAC. The prototype chip is implemented in 180nm CMOS technology, and it is capable of reading out both AC and DC responses. The measurement results prove that the proposed architecture achieves the highest THD among previously reported sensor readout ICs.

#### ACKNOWLEDGMENT

The chip fabrication and the EDA tools were supported by the IC Design Education Center.

## REFERENCES

- [1] H. Chandrakumar and D. Markovic, "An 80-mVpp linear-input range, 1.6-G $\Omega$  input impedance, low-power chopper amplifier for closed-loop neural recording that is tolerant to 650-mVpp common-mode interferences," *IEEE J. Solid-State Circuits*, vol. 52, no. 11, pp. 2811-2828, Nov. 2017.

- [2] T. Denison, K. Consoer, and W. Santa, "A 2uW 100nV/√Hz chopper stabilized instrumentation amplifier for chronic measurement of neural field potentials," *IEEE J. Solid-State Circuits*, vol.42, no. 12, pp. 2934-2945, Dec. 2007.

- [3] A. Sukumaran and S. Pavan, "Low power design techniques for single-bit audio continuous-time delta sigma ADCs using FIR feedback," *IEEE J. Solid-State Circuits*, vol.49, no. 11, pp. 2514-2525, Nov. 2014.

- [4] J. Lim, Y. Cho, K. Jung, J. Park, J. Choi and J. Kim, "A wide-band active-RC filter with a fast tuning scheme for wireless communication receivers," *IEEE Custom Integr. Circuits Conf.*, Sep. 2005, pp. 637-640.

- [5] J. Lim, S. Park, J. Kang, and S. Kim, "A 22-bit read-out IC with 7-ppm INL and sub-100-uHz 1/f corner for DC measurement systems," *IEEE J. Solid-State Circuits*, vol.54, no. 11, pp. 3086-3096, Nov. 2019.

- [6] H. Jiang, S. Nihtianov, and K. A. A. Makinwa, "An energy-efficient 3.7 nV/√Hz bridge readout IC with a stable bridge offsets compensation scheme," *IEEE J. Solid-State Circuits*, vol.54, no. 3, pp. 856-864, Mar. 2019.

- [7] H. Jiang, C. Ligouras, S. Nihtianov, and K. A. A. Makinwa, "A 4.5 nV/√Hz capacitively coupled continuous-time sigma-delta modulator with an energyefficient chopping scheme," *IEEE Solid-State Circuits Lett.*, vol. 1, no. 1, pp. 18-21, Jan. 2018.

- [8] C.-C. Tu, Y.-K. Wang, and T.-H. Lin, "A 0.06 mm<sup>2</sup> ±50 mV range -82 dB THD chopper VCO-based sensor readout circuit in 40 nm CMOS," in *Proc. Symp. VLSI Circuits, Kyoto, Japan*, 2017, pp. C84-C85.

- [9] J. Bang, H. Jeon, M. Je, and G. Cho, "A 6.5 uW 92.3 dB-DR biopotential-recording front-end with 360 mVpp linear input range," in *Proc. Symp. VLSI Circuits, Kyoto, Japan*, 2018, pp. 239-240.

- [10] W. Zhao, S. Li, B. Xu, X. Yang, L. Shen, N. Lu, D. Z. Pan, and N. Sun, "A 0.025-mm<sup>2</sup> 0.8-V 78.5-dB SNDR VCO-based sensor readout circuit in a hybrid PLL-ΔΣM structure," *IEEE J. Solid-State Circuits*, vol. 55, no. 3, pp. 666-679, Mar. 2020.

**Chae Gang Lim** (S'14) received the B.S. degrees in electrical engineering from Korea University, Seoul, South Korea, in 2014, where he is currently working toward an integrated M.S. And Ph. D. degree.

In 2017, he was a Visiting Researcher at the University of Texas at Austin, TX, USA. He received the 21st Korea Semiconductor Design Contest enterprise special prize

(Cadence) in 2020. His research interests include sensor readout ICs and oversampling ADCs.

**Chul Woo Kim** (S'98-M'02-SM'06) received the B.S. and M.S. degrees in electronics engineering from Korea University in 1994 and 1996, respectively, and a Ph. D. in electrical and computer engineering from the University of Illinois at Urbana-Champaign, IL, USA, in 2001.

In 1999, he worked as a summer intern at the Design Technology at

Intel Corporation, Santa Clara, CA. In May 2001, he joined IBM Microelectronics Division, Austin, TX, where he was involved in Cell processor design. Since September 2002, he has been with the School of Electrical Engineering, Korea University, where he is currently a Professor. He was a Visiting Professor at the University of California at Los Angeles in 2008 and at the University of California at Santa Cruz in 2012. He is a coauthor of two books, namely, CMOS Digital Integrated Circuits: Analysis and Design (McGraw Hill, 4th edition 2014) and High-Bandwidth Memory Interface (Springer, 2013). His current research interests are in the areas of wireline transceiver, memory, power management and data converters.

Dr. Kim received the Samsung HumanTech Thesis Contest Bronze Award (1996), the ISLPED Low-Power Design Contest Award (2001, 2014), the DAC Student Design Contest Award (2002), SRC Inventor Recognition Awards (2002), the Young Scientist Award from the Ministry of Science and Technology of Korea (2003), the Seoktop Award for excellence in teaching (2006, 2011) and ASP-DAC Best Design Award (2008) and Special Feature Award (2014), Korea Semiconductor Design Contest: Prime Minister Award (2016). He served on the Technical Program Committee of the IEEE International Solid-State Circuits Conference and as a Guest Editor for IEEE Journal of Solid-State Circuits. He is currently on the editorial board of IEEE Transactions on VLSI Systems and the Chair of the SSCS Seoul Chapter. He has been elected as Distinguished Lecturer of the IEEE Solid-State Circuits Society for 2015– 2016.