# A 2.4 GHz Low Power Low-IF Receiver Employing OOK and FSK Dual-Mode Demodulator for IoT Applications

# Myung Hun Lee and Ku Duck Kwon<sup>a</sup>

Department of Electronics Engineering and Department of BIT Medical Convergence, Kangwon National University E-mail: kdkwon@kangwon.ac.kr

Abstract – In this paper, a 2.4 GHz low-power low-IF receiver employing a dual-mode demodulator for on-off keying (OOK) and frequency-shift keying (FSK) signals is presented for Internet of Things (IoT) applications. The switched dual-mode demodulator can demodulate both OOK and FSK signals. The proposed receiver consists of a low-noise transconductance amplifier, single-balanced current-mode passive mixer, transimpedance amplifier, variable gain amplifier, and dual-mode demodulator. The proposed receiver was designed in a 65-nm CMOS process and mainly simulated at 2.4 GHz. The receiver achieves a noise figure of 9.9 dB, a maximum conversion gain of 74 dB, and an input-referred third-order intercept point of —26.3 dBm. The active die area of the designed receiver is 0.53 mm², and it draws a bias current of 1.8 mA from a nominal supply voltage of 1 V.

Keywords—2.4 GHz, Dual-mode demodulator, Frequency-shift keying (FSK), IoT, Low-power, On-Off Keying (OOK)

#### I. INTRODUCTION

The Internet of Things (IoT) is a technology that collects, stores, and analyzes data using sensors and communication on various devices. Developing a technology that can be used permanently without battery replacement is one of the most important issues in IoT sensors. Generally, a wireless communication system is the most power-consuming block in IoT sensors. In order to minimize the power consumption of the wireless communication system, researches on the duty-cycle-based transceiver architecture that turns on the transceiver only at a certain time and the transceiver architecture based on the ultra-low power wake-up radio are being actively conducted [1]–[4]. Because IoT transceivers do not require a high data rate, simple modulation schemes such as on-off keying (OOK) or frequency-shift keying (FSK) are mainly used.

In this paper, a 2.4 GHz low-power low-IF receiver employing a dual-mode demodulator, which can demodulate both OOK and FSK signals is proposed for IoT applications. Section II presents the proposed low-power low-IF receiver

a. Corresponding author; kdkwon@kangwon.ac.kr

Manuscript Received June 26, 2021, Revised September 12, 2021, Accepted Sep. 16, 2021

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<a href="http://creativecommons.org/licenses/bync/3.0">http://creativecommons.org/licenses/bync/3.0</a>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

architecture and detailed circuit designs. Simulation results are shown in Section III. Finally, Section IV concludes the paper.

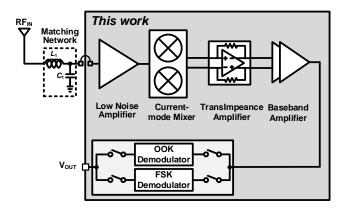

Fig. 1. Block diagram of the proposed receiver.

## II. CIRCUIT IMPLEMENTATION

Fig. 1 shows the block diagram of the proposed low-power low-IF receiver with a dual-mode demodulator. The proposed receiver consists of a low-noise transcondutance amplifier (LNTA), single-balanced current-mode passive mixer, transimpedance amplifier (TIA), variable gain amplifier (VGA), and dual-mode demodulator.

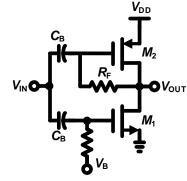

A current-reused resistive feedback LNTA is shown in Fig. 2. The resistive feedback LNTA can perform an input impedance matching without a bulky degeneration on-chip inductor. The current-reuse technique increases the voltage gain and reduces the noise figure (NF) with the same current consumption as the conventional common-source (CS) amplifier because the effective transconductance  $(g_m)$ becomes  $g_{m1} + g_{m2}$  [5]. The  $R_F$  provides the real part of the resistive feedback LNTA input impedance. The gate biasing for  $M_1$  and  $M_2$  are separated to support low supply voltage. [6]. The proposed RF LNTA also adopts an input matching network composed of  $L_I$  and  $C_I$  to take advantage of the gain-boosting property of an inductor-degenerated CSLNA (L-CSLNA). The input impedance of the RF LNTA  $R_{IN\ RFLNTA}$  is  $(R_F + R_{oLNTA}) / (1 + g_{mLNTA}R_{oLNTA})$ , where  $g_{mLNTA}$ is  $g_{m1} + g_{m2}$  and  $R_{oLNTA}$  is  $r_{o1} / / r_{o2} / / R_{IN\ MIXER}$ . The equivalent input matching network can be converted from a parallel RC to series RC network with a narrow frequency band of interest. Therefore, the proposed RF LNTA performs input power matching with a series RLC network. The overall  $g_m$  of the proposed RF LNTA is effectively boosted by  $\sqrt{(1+Q^2)}$  [7]. The series capacitance  $C_{SER}$  and series resistance  $R_{SER}$  in the converted series RLC network are expressed as  $(C_{gs} + C_I)(1 + 1/Q_L^2)$  and  $(R_F + R_{oLNTA}) / [(1 + g_{mLNTA}R_{oLNTA})(1 + Q_L^2)]$ , respectively. When the  $L_I$  and  $C_{SER}$  values are set to resonate at 2.4 GHz, the input impedance of the proposed LNTA is  $R_{SER}$ , which is equal to a source resistance  $R_S$ . Therefore,  $Q_L$  is  $\omega_o L_I/R_S$  for the operation frequency of  $\omega_o$ . The overall transconductance of the proposed LNTA from  $V_S$  to the LNTA output current is given to

$$G_{mLNTA} = \frac{\sqrt{1 + Q_L^2}}{2} \left( g_{mLNTA} - \frac{1}{R_F} \right) \approx \frac{\sqrt{1 + Q_L^2}}{2} g_{mLNTA} \qquad (1)$$

It can be known from (1) that the current-reused RF LNTA has a large effective transconductance.

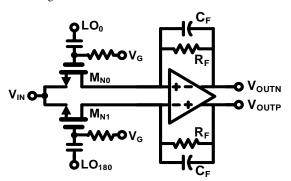

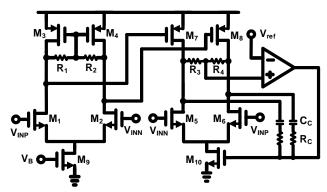

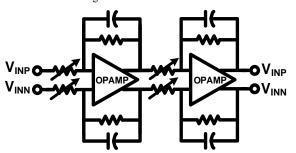

The current-mode single-balanced passive mixer with 50 % duty-cycle local oscillator signal is used for downconversion. It is shown in Fig. 3. An operational amplifier (OPAMP)-based TIA is used for current-to-voltage conversion and the first-order OB blocker filtering. A modified feedforward (FF) op-amp is utilized due to its inherent wideband characteristic [8]. From the FF op-amp, an intrinsic zero from the FF path compensates the phase of the op-amp without Miller capacitance and accordingly extends the bandwidth of the op-amp. Fig. 4 shows a schematic of a modified FF OPAMP. As the main and FF paths are depicted in Fig. 4, the first, second, and FF amplifier stages are given by  $M_{1-2}$ ,  $M_{7-8}$ , and  $M_{5-6}$ , respectively. It is noted that the second stage also acts as an active load of the FF stage so that the extra second stage with a separate current branch is not necessary. Therefore, the internal poles and zeros generated by the parasitic can be

Fig. 2. Current-reused resistive-feedback LNTA

Fig. 3. Single-balanced current-mode passive mixer with TIA

reduced, and this improves the bandwidth of the modified FF structure. The small input impedance of the TIA can limit the voltage swing at the input and output of the mixer which enhances the linearity.

The conversion gain of the receiver RF front-end from  $V_S$  to the TIA output voltage is expressed as

$$A_{VRFFE} \approx \frac{\sqrt{1 + Q_L^2}}{\pi} g_{mLNTA} R_{FTIA}$$

(2)

where  $R_{FTIA}$  is a feedback resistor of the TIA.

Fig. 4. Modified FF OPAMP

Fig. 5. Two-stage OPAMP-based VGA

The schematic of VGA is presented in Fig. 5. The two-stage OPAMP-based baseband amplifier is designed to have sufficient gain and dynamic range. The FF OPAMP shown in Fig. 4 is also used in VGA.

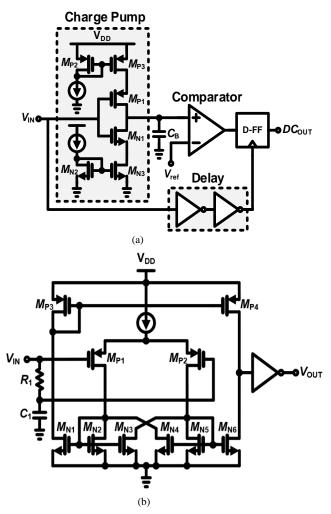

A switched dual-mode demodulator supporting both OOK and FSK demodulations is presented in Fig. 6. The demodulator scheme is selected according to the input modulation signal. The schematic of the FSK demodulator is presented in Fig. 6(a). The energy charging capacitor  $C_B$  is charged and discharged with on-and-off operations of M<sub>P1</sub> and M<sub>N1</sub>. If the input frequency is high, each charging and discharging time will be short, resulting in a low charged voltage across  $C_B$ . On the other hand, at the low input frequency, the higher voltage is charged in  $C_B$ . The comparator compares  $V_{ref}$  with the voltage across  $C_B$ . The comparator generates a rail-to-rail signal in the low input frequency and a zero voltage signal in the high input frequency. The comparator output voltage and delayed FSK signal are the input signal and clock of D flip-flop, respectively. Because the delayed input signal is used as the clock signal, an additional external clock is not required. The OOK demodulator is shown in Fig. 6(b). The OOK demodulator compares the OOK input signal and the lowpass filtered OOK signal and determinen logic 0 and 1.

#### III. SIMULATION RESULTS

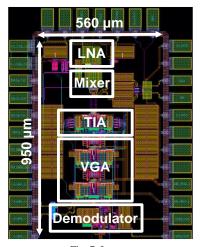

The proposed 2.4GHz low power low-IF receiver with a switched dual-mode demodulator was designed and simulated in a 65-nm process. The layout is shown in Fig. 7. The active area is 0.53 mm<sup>2</sup> excluding the bond pads. It consumes 1.8 mW at a supply voltage of 1V. The power breakdown of the proposed receiver according to the operating modes is shown in Table I.

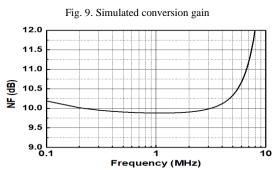

Fig. 8 shows simulated S11 of the designed receiver. The receiver obtained S11 of less than 10 dB in the frequency range of 2-2.7 GHz. The simulated conversion gain of the receiver is depicted in Fig. 9. The conversion gain of 74 dB is obtained. The simulated NF of the receiver is illustrated in

TABLE I. Simulated Power Breakdown

|       | Power Consumption<br>(OOK) | Power Consumption<br>(FSK) |  |  |  |

|-------|----------------------------|----------------------------|--|--|--|

| LNA   | 1 mW                       |                            |  |  |  |

| TIA   | 0.2 mW                     |                            |  |  |  |

| VGA   | 0.4 mW                     |                            |  |  |  |

| DMD   | 0.15 mW                    | 0.2 mW                     |  |  |  |

| Total | 1.75 mW                    | 1.8 mW                     |  |  |  |

Fig. 6. (a) FSK Demodulator (b) OOK Demodulator

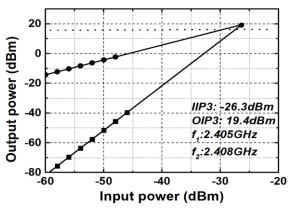

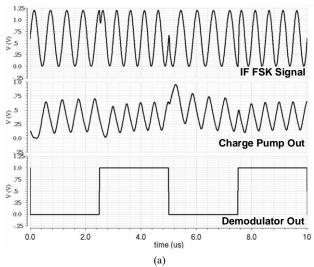

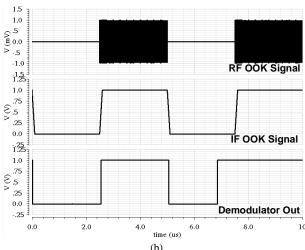

Fig. 10. The obtained NF at the IF frequency of 2 MHz is 9.9 dB. The simulated input-referred third-order intercept points (IIP3) is shown in Fig. 11. The two-tone test conditions for IIP3 are  $f_1 = f_{LO} + 5$  MHz and  $f_2 = f_{LO} + 8$  MHz. The simulated IIP3 of -26.3 dBm is obtained. The simulated transient response of the receiver according to the modulated signals are shown in Fig. 12. The designed dual-mode demodulators can demodulate both OOK and FSK signals.

Fig. 7. Layout

-5

-10

-20

-25

-2 2.2 2.4 2.6 2.8

Frequency (GHz)

Fig. 8. Simulated S11

80

90

100

75

65

2 2.2 2.4 2.6 2.8

Frequency (GHz)

Fig. 10. Simulated NF

Fig. 11. Simulated IIP3

Fig. 12. Simulated transient response: (a) FSK (b) OOK

Table II summarizes the simulated performances of the designed receiver and compares them with those of state-of-the-art receivers. We use a figure of merit (FOM), which is defined as

$$FoM(dB) = -P_{SEN}(dBm) - 10\log \frac{P_{dc}}{1 \text{ mW}}.$$

(3)

This work can support dual-mode demodulations while achieving the similar sensitivity performance and FOM.

TABLE II. Performance Summary and comparison with previous works

| Reference                       | [9]          | [10]         | [11]         | [12]         | [13]          | This<br>Work* |

|---------------------------------|--------------|--------------|--------------|--------------|---------------|---------------|

| Operating<br>Frequency<br>(GHz) | 5.5-5.8      | 0.915        | 2.4          | 2.44         | 5.8           | 2.44          |

| Process                         | 40nm<br>CMOS | 55nm<br>CMOS | 40nm<br>CMOS | 65nm<br>CMOS | 40nm<br>CMOS  | 65nm<br>CMOS  |

| Modulation                      | ООК          | BFSK         | FSK          | FSK          | OOK/<br>FSK   | OOK<br>/FSK   |

| Power (mW)                      | 0.217        | 0.499        | 1.2          | 0.22         | 0.47/<br>0.49 | 1.75/1.8      |

| Bandwidth (MHz)                 | 2            | 1            | 2            | 2            | 1             | 2.4           |

| NF(dB)                          | 17           | N/A          | 9            | 22.6         | 12            | 9.9           |

| Sensitivity (dBm)               | -82          | -99          | -82.2        | -85          | -90           | -89           |

| Area (mm²)                      | 0.151        | 2.25         | 1            | 2.4          | 0.166         | 0.53          |

| FOM<br>(dB)                     | 88.64        | 99.01        | 81.41        | 91.58        | 90.27         | 86.57         |

<sup>\*</sup>Simulation Results

#### IV. CONCLUSION

A 2.4 GHz low-power low-IF receiver employing a dual-mode demodulator for OOK and FSK signals is designed in 65-nm CMOS process for IoT applications. The proposed switched dual-mode demodulator can demodulate both OOK and FSK signals. The designed receiver achieves a NF of 9.9 dB, maximum conversion gain of 74 dB, and IIP3 of -26.3 dBm.

### ACKNOWLEDGMENT

This work was supported in part by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education under Grant NRF-2018R1D1A1B07042804, in part by the Ministry of Science and ICT, South Korea, through the Information Technology Research Center Support Program supervised by the Institute for Information and Communications Technology Promotion (IITP) under Grant IITP-2021-2018-0-01433, and in part by the chip fabrication and fabrication and EDA tool by the IC Design Education Center (IDEC).

# REFERENCES

- [1] O. Abdelatty, H. Bishop, Y. Shi, D. Chen, A. Alghaihab, B. Calhoun and D. Wentzloff, "A low power Bluetooth low-energy transmitter with a 10.5nJ startup-energy crystal oscillator," in *IEEE European Solid-State Circuits Conf.* (ESSCIRC), 2019, pp. 377–380.

- [2] J. Brown, K. Huang, E. Ansari, R. Rogel, Y. Lee and D. Wentzloff, "An ultra-low-power 9.8 GHz crystal-less UWB transceiver with digital baseband integrated in 0.18µm

- BiCMOS," in *IEEE Int. Solid-State Circuits Conf. Tech. Dig.*, San Francisco, CA, Feb. 2013, pp. 442-443.

- [3] K. Cheng and S. Chen, "An Ultralow-power wake-up receiver based on direct active RF detection," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 7, pp. 1661-1672, July 2017.

- [4] C. Bryant and H. Sjöland, "A 2.45 GHz, 50 μW wake-up receiver front-end with -88 dBm sensitivity and 250 kbps data rate," in *IEEE European Solid State Circuits Conf.* (ESSCIRC), 2014, pp. 235–238.

- [5] A. Karanicolas, "A 2.7-V 900-MHz CMOS LNA and mixer," IEEE J. Solid-State Circuits, vol. 31, no. 12, pp. 1939-1944, Dec. 1996.

- [6] T. Kim, D. Im and K. Kwon, "360-μW 4.1-dB NF CMOS MedRadio receiver RF front-end with current-reuse Q-boosted resistive feedback LNA for biomedical IoT applications." *Int. J. Circuit Theory Appl.* vol. 48, no. 4, pp. 502-511, April 2020.

- [7] S. Joo, T. Choi and B. Jung., "A 2.4-GHz Resistive Feedback LNA in 0.13-um CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 11, pp. 3019-3029, Nov. 2009.

- [8] K. Kwon, "A 40 M 1000 MHz 77.2 dB spurious free dynamic range CMOS RF variable gain amplifier for digital TV tuner ICs," *Int. J. Circuit Theory Appl.*, vol. 43, no. 7, pp. 875-886, July 2015.

- [9] J. Im, H. Kim and D. Wentzloff, "A 217μW –82 dBm IEEE 802.11 Wi-Fi LP-WUR using a 3rd-harmonic passive mixer," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2018, pp. 172-175.

- [10] K. Kim, E. Jeong and K. Choi., "A 915 MHz, 499 µW, –99 dBm, and 100 kbps BFSK direct conversion receiver," in *IEEE European Solid State Circuits Conf.* (ESSCIRC), 2019, pp. 209-212.

- [11] A. Alghaihab, Y. Shi, J. Breiholz, H. Kim, B. Calhoun, and D. Wentzloff, "Enhanced interference rejection Bluetooth low-energy back-channel receiver With LO frequency hopping," IEEE J. Solid-State Circuits, vol. 54, no. 7, pp. 2019-2027, July 2019.

- [12] P. Wang and P. Mercier, "An interference-resilient BLE-compatible wake-up receiver employing single-die multi-channel FBAR-based filtering and a 4-D wake-up signature," *IEEE J. Solid-State Circuits*, vol. 56, no. 2, pp. 416-426, Feb. 2021.

- [13] J. Im, H. Kim and D. Wentzloff, "A 470μW -92.5 dBm OOK/FSK receiver for IEEE 802.11 WiFi LP-WUR," in *IEEE European Solid State Circuits Conf.* (ESSCIRC), 2018, pp. 302-305.

Myung Hun Lee received the integrated B.S. and M.S. degree from the Department of Electronics Engineering, Kangwon National University, Chuncheon, Korea, in 2019 and 2021, respectively. In 2021, joined Samsung he Electronics Company Ltd., Hwaseong, South Korea. His research interests include CMOS RF/analog integrated circuits and

RF system design for wireless communications. He was a recipient of Ministry of Trade, Industry and Energy award for Korea Semiconductor Design Competition in 2019 and 3rd award for 11th ETNEWS ICT best paper award in 2019.

Ku Duck Kwon received the B.S. and Ph.D. degrees in Electrical Engineering and Computer Science from Korea Advanced Institute of Science and Technology (KAIST), in Daejeon, South Korea, in 2004 and 2009, respectively. His doctoral research concerned digital TV tuners and dedicated short-range communication (DSRC) systems.

From 2009 to 2010, he was a Post-Doctoral Researcher with KAIST, where he studied a surface acoustic wave (SAW)-less receiver architectures and developed 5.8GHz RF transceivers for DSRC applications. From 2010 to 2014, he was a Senior Engineer with Samsung Electronics Co. LTD., Suwon, South Korea, where he has been involved with studies of the SAW-less software-defined receivers and development of CMOS transceivers for 2G/3G/4G cellular applications and receivers for universal silicon tuners. In 2014, he joined the Department of Electronics Engineering, Kangwon National University, Chuncheon, South Korea, where he is currently an Associate Professor. His research interests include CMOS mmWave/RF/analog integrated circuits and RF system design for wireless communications.