# A High-Efficiency Hybrid Buck-Boost Photovoltaic Energy Harvester with Adaptive Fractional Open-Circuit Voltage Maximum-Power-Point-Tracking Control

Phan Dang Hung<sup>1</sup>, Van Thai Trinh<sup>2</sup>, Yechan Park<sup>2</sup>, Minkyu Je<sup>2</sup>

<sup>1</sup>Samsung Electronics, South Korea

<sup>2</sup>KAIST, South Korea

E-mail: hungphandang 1994@gmail.com

Abstract-This paper presents an energy-efficient photovoltaic energy harvesting system achieving an ultra-wide input power (P<sub>IN</sub>) range by optimizing both maximum-power-point-tracking efficiency (nmppt) and power-conversion efficiency (nconv). An MPPT based on an adaptive fractional open-circuit voltage method is proposed to tune the fraction k based on  $P_{IN}$  with only little power overhead, unlike other complex and power-hungry hybrid MPPTs. Also, the harvester maintains high  $\eta_{CONV}$  at low  $P_{IN}$ levels thanks to its modified hybrid topology that operates as a buck-boost converter with three different control techniques. The proposed zero-current detection circuit reduces the control bit size and response time because it actively changes the tuning resolution according to P<sub>IN</sub>. The proposed system achieves  $\eta_{MPPT} > 98\%$  across a 10,000× P<sub>IN</sub> dynamic range, and the achieved η<sub>CONV</sub> is greater than 81% across the whole range with a peak efficiency of 96.5%. Compared to other previous state-of-the-art works, this design provides the highest peak nconv as well as the widest Pin ranges, over which it achieves >98%  $\eta_{MPPT}$  and >80%  $\eta_{CONV}$ .

Keywords—Photovoltaic energy harvesting (PV EH), maximum power point tracking (MPPT), adaptive fractional open-circuit voltage (FOCV), hybrid converter, zero current detection (ZCD).

# I. INTRODUCTION

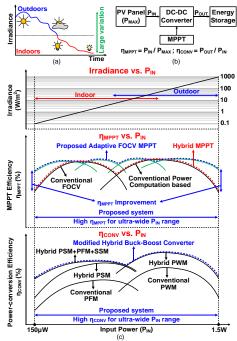

Demand for modern mobile devices has grown rapidly to fulfill human daily lives and activities. Most of these devices are battery-powered, and battery life has always been a big challenge. Photovoltaic (PV) energy harvesting (EH) has been widely used to extend the battery usage time [1]. However, the power harvested from the PV panels greatly depends on the ambient irradiance. Because mobile devices require to operate both outdoors and indoors, the exposed irradiance of PV panels has a large variation (Fig. 1(a)). Due to such irradiance-level variations, the available power from a PV panel with a size of a touchscreen can vary from hundreds of  $\mu W$  to a W [2].

Fig. 1(b) shows a block diagram of conventional PV EH systems. The energy is harvested from a PV panel and delivered to an energy storage device, such as a battery. For this EH process, a DC-DC converter is used in between to control the

a. Corresponding author; <a href="https://hungphandang@gmail.com">hungphandang@gmail.com</a>

Manuscript Received Aug. 30, 2025, Revised Nov. 16, 2025, Accepted Nov. 17, 2025

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<a href="http://creativecommons.org/licenses/by-nc/4.0">http://creativecommons.org/licenses/by-nc/4.0</a>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

operating point of the PV panel and maximize the harvested energy. The maximum possible amount of energy can be harvested from the PV panel by employing a maximum-power-point-tracking (MPPT) method. The end-to-end efficiency can be calculated as the product of the maximum-power-point-tracking efficiency ( $\eta_{MPPT}$ ) and power-conversion efficiency ( $\eta_{CONV}$ ). However, this maximum power point (MPP) varies over the wide power range of the PV panel [2]. Thus, the MPP should be adaptively found and followed continuously over a wide range to maximize  $\eta_{MPPT}$  and  $\eta_{CONV}$  concurrently.

There are various types of MPPT methods including fractional open-circuit voltage (FOCV), hill climbing, perturb/observe (P&O), and global search. However, most of the integrated energy harvesters use only one MPPT method for wide irradiance levels [2]. As shown in Fig. 1(c, middle), those energy harvesters with power computation-based MPPT schemes [3], [4] are susceptible to errors not only in the current sensing but also in the computation by multiplication circuitry, thereby degrading the MPPT efficiency, especially, under low input power levels. Since conventional FOCV methods [1], [5] offer high MPPT efficiency across a very narrow power range only due to their limited fractional-constant accuracy. The hybrid MPPT method [2] can improve  $\eta_{MPPT}$  but at the cost of complexity and power consumption. Also,  $\eta_{MPPT}$  at both ends of the P<sub>IN</sub> range is still very low. To address these issues, we propose an adaptive FOCV MPPT method (Fig. 1(c, middle)) that tunes the fraction k depending on the measured open-circuit voltage (V<sub>OC</sub>) output of the PV panel.

The main power loss (P<sub>LOSS</sub>) in a DC-DC converter consists of conduction loss (P<sub>COND</sub>), switching loss (P<sub>SW</sub>), and quiescent loss (P<sub>0</sub>) [6]. As shown in Fig. 1(c, bottom), under high P<sub>IN</sub> conditions, the conventional PV EH designs [1] - [4] have limited  $\eta_{\text{CONV}}$  because of the significantly high  $P_{\text{COND}}$  incurred by large DCR of the inductor (R<sub>DCR</sub>) [7]. The previous harvesters [2], [5] have low  $\eta_{CONV}$  under low  $P_{IN}$  levels due to high Psw and Po caused by using the same size of the power switches and a single switching technique. To overcome these challenges, we propose to use a new hybrid buck-boost topology modified from [7]-[8]. Here a pulse width modulation (PWM) [2] is adopted in the buck mode, while in the boost mode, a pulse skipping modulation (PSM) [9] is implemented in conjunction with a pulse frequency modulation (PFM) [9] and a switch size modulation (SSM) [10]. Thanks to all of these, the proposed work can provide high  $\eta_{CONV}$  across an ultra-wide P<sub>IN</sub> range.

Fig. 1. (a) Irradiance variation profile of a PV panel. (b) Conventional PV energy harvesting system. (c) Comparison of the proposed and conventional energy harvesters in terms of the MPPT efficiency and power-conversion efficiency.

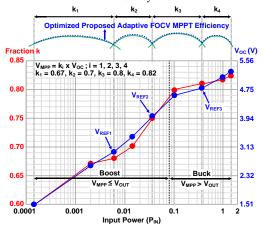

Fig. 2. Measured PV panel characteristics

## II. PROPOSED PHOTOVOLTAIC ENERGY HARVESTER

The measured characteristics of the PV panel we used are shown in Fig. 2. The PV panel is built from three 8.9 cm  $\times$  5.5 cm monocrystalline PV modules connected in parallel. The measurements are performed under both indoor and outdoor environments that can provide  $P_{\rm IN}$  from 150  $\mu$ W to 1.5 W for the PV EH system. The blue line shows  $V_{\rm OC}$  over  $P_{\rm IN}$ , and  $V_{\rm OC}$  varies from 1.5 V to 5.2 V for the range 150  $\mu$ W to 1.5 W. The red line shows the fraction k over the variation of  $P_{\rm IN}$ , and k changes from 0.60 to 0.83 over the range.

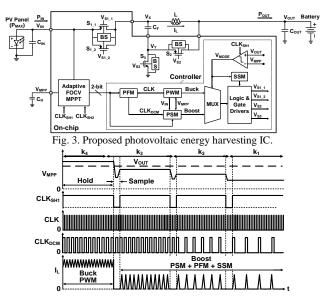

Fig. 3 shows the proposed PV EH system consisting of a PV panel, a battery, and the proposed hybrid buck-boost converter with an adaptive FOCV MPPT block and a controller. The converter is composed of three 5-V power switches ( $S_1$ , which is separated to  $S_{1\_1}$  and  $S_{1\_2}$  for SSM,  $S_2$ , and  $S_3$ ) employing the body-switching (BS) technique [8], a flying capacitor ( $C_F$ ), and

Fig. 4. System operation scheme when the irradiance decreases.

an inductor (L). The MPPT block samples the MPPT voltage (VMPP) and compares it with Vout to concurrently carry out EH and the mode detection. As illustrated in Fig. 4, when VMPP  $\leq$  Vout, the system operates in the boost mode. Otherwise, it operates in the buck mode. A dynamic comparator operated with a low-frequency clock (CLK\_{SH1}) is used to detect the mode with only a little power. A 2b output from the MPPT block is used for the PSM and PFM controls. Fig. 4 depicts the system operation scheme for a case when the irradiance decreases. The sample and hold clock (CLK\_{SH1}) for the MPPT and the switching clock (CLK) for the PWM control are fixed at 1/12 Hz and 1 MHz, respectively. The irradiance level is monitored periodically at CLK\_{SH1}, and based on the level, CLK\_{DCM} and the control mode in the boost mode are controlled to minimize  $P_{LOSS}$  at low  $P_{IN}$  levels.

#### III. CIRCUIT IMPLEMENTATIONS

# A. Proposed Adaptive FOCV MPPT

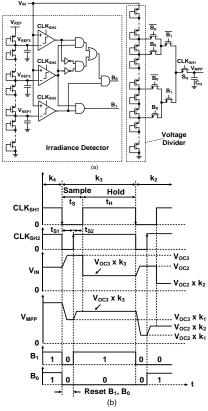

Fig. 5 shows the proposed adaptive FOCV MPPT block. An irradiance detector converts Voc into a 2b digital signal (B<sub>1</sub>, B<sub>0</sub>) that represents 4 P<sub>IN</sub> regions. For each region, an optimized k is decided and used, as indicated in Fig. 2. To find the optimized k, k of the PV panel is swept to maximize the lowest  $\eta_{MPPT}$  in all P<sub>IN</sub> ranges. During the sample period (Sh: on), the 2b digital signal (B<sub>1</sub>, B<sub>0</sub>) is reset to 0, V<sub>IN</sub> rises towards Voc, and its initial fraction V<sub>MPP</sub> (= k<sub>1</sub> × Voc) is sampled on Ch. At the CLKsh2 rising edge, the irradiance detector compares V<sub>IN</sub> with V<sub>REF1</sub>, V<sub>REF2</sub>, and V<sub>REF3</sub> to detect the P<sub>IN</sub> level. In Fig. 2, the V<sub>REF</sub> values are defined from the open-circuit voltage (V<sub>OC</sub>) at the crossing point of the four MPPT efficiency plots for k<sub>1</sub>, k<sub>2</sub>, k<sub>3</sub>, and k<sub>4</sub>. Then, V<sub>MPP</sub> is changed to the corrected V<sub>MPP</sub> (= k<sub>1</sub> × V<sub>OC</sub>). During the hold period (Sh: off), the corrected V<sub>MPP</sub> is held on Ch while the converter harvests the energy.

The voltage dividers for creating the fractions of  $V_{OC}$  and the reference voltages of the irradiance detector are implemented using diode-connected low-threshold-voltage 5-V PMOS

Fig. 5. Proposed adaptive FOCV MPPT block: (a) circuit diagram and (b) waveforms of the main signals.

transistors, as shown in Fig. 5(a). In the irradiance detector, dynamic comparators [11] are adopted to reduce power consumption as it does not consume quiescent power, unlike analog continuous-time comparators. The total sample time  $t_{\rm S}$  (= 0.4 seconds) is chosen in consideration of the power consumed by the voltage divider, that is the main power consumption of the MPPT circuit. The sample time  $t_{\rm S1}$  (= 0.2 second) and  $t_{\rm S2}$  (= 0.2 second) are decided considering the time for  $V_{\rm MPP}$  to rise or fall to the proper values over all  $P_{\rm IN}$  ranges. Because the accuracy of  $V_{\rm MPP}$  directly affects  $\eta_{\rm MPPT}$ , the hold time  $t_{\rm H}$  (= 11.6 seconds) is designed considering  $V_{\rm MPP}$  deviations caused by the leakage from  $C_{\rm H}$  (= 10 nF).

# B. Proposed Hybrid Buck-Boost Converter and Control Circuits

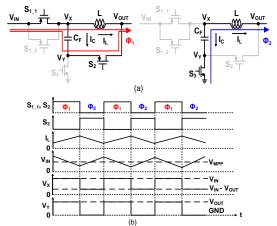

Fig. 6 shows the buck mode operation. During  $\Phi_1$  ( $S_{1\_1}$ ,  $S_2$ : on;  $S_{1\_2}$ ,  $S_3$ : off), the inductor current (IL) ramps up, CF is charged to  $V_{IN}-V_{OUT}$ , and  $V_{OUT}$  is supplied by the dual paths of IL and the current of  $C_F$  (Ic). During  $\Phi_2$  ( $S_3$ : on;  $S_{1\_1}$ ,  $S_{1\_2}$ ,  $S_2$ : off), L and CF are connected in series, and Ic is set to  $-I_L$  since  $I_L$  acts like a current source, supplying  $V_{OUT}$ . In comparison to the conventional designs, the dual path topology greatly reduces  $P_{COND}$  in the inductor, thus improving  $\eta_{CONV}$  [7]. The boost mode operation is shown in Fig. 7. During  $\Phi_1$  ( $S_2$ : on;  $S_{1\_1}$ ,  $S_{1\_2}$ ,  $S_3$ : off), CF behaves like a voltage source building up IL. During  $\Phi_2$  ( $S_{1\_1}$ ,  $S_{1\_2}$ ,  $S_3$ : on;  $S_2$ : off), IL supplies  $V_{OUT}$  and decreases because  $V_{OUT}$  is larger than  $V_{IN}$ . At the same time, CF is charged to  $V_{IN}$ . During  $\Phi_3$  ( $S_{1\_1}$ ,  $S_{1\_2}$ ,  $S_2$ ,  $S_3$ : off), the converter is idle, and the voltage on CF is held at around  $V_{IN}$ . Because this topology needs fewer power switches than conventional buck-

Fig. 6. Buck mode operation: (a) circuit diagram and (b) waveforms of the main signals.

Fig. 7. Boost mode operation: (a) circuit diagram and (b) waveforms of the main signals.

boost converters and only one switch exists in the main current path, it can achieve lower power loss and smaller chip size [8].

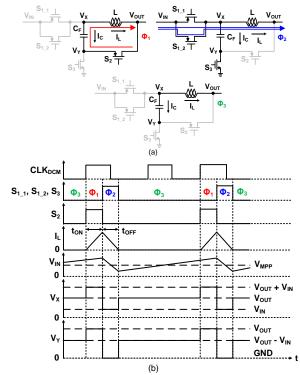

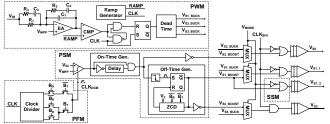

The control circuit of the hybrid buck-boost converter is depicted in Fig. 8. In the buck mode, the PWM controller with a type III compensator is adopted to operate the system in continuous conduction mode (CCM). During this mode, the input voltage  $V_{\rm IN}$  is regulated by the PWM controller to ramp down to match  $V_{\rm MPP}$  at high  $P_{\rm IN}$ . In the boost mode, the PSM controller operates the system in discontinuous conduction mode (DCM). The PSM controller regulates  $V_{\rm IN}$  to  $V_{\rm MPP}$  as follows. During the hold period of  $CLK_{\rm SH1}$  ( $T_{\rm H}$  in Fig. 5(b)), the converter harvests the energy from the PV panel, as mentioned in Section III-A. The operation diagram of the converter operating in the boost mode is shown in Fig. 7(b). At the rising edges of the PSM clock ( $CLK_{\rm DCM}$ ), if  $V_{\rm IN} > V_{\rm MPP}$ , the converter starts to harvest energy from the PV panel. During this period,

Fig. 8. The control circuits of the hybrid buck-boost converter.

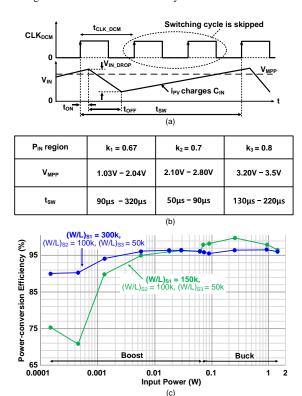

Fig. 9. (a) Example voltage waveform of  $V_{\rm IN}$  with  ${\rm CLK_{DCM}}$  when using the PSM. (b) Simulated switching period without the PFM for three different  $P_{\rm IN}$  regions. (c) Power-conversion efficiency improvement by the switch size modulation.

| P <sub>IN</sub> region | k <sub>1</sub> = 0.67 | k <sub>2</sub> = 0.7 | k <sub>3</sub> = 0.8 |

|------------------------|-----------------------|----------------------|----------------------|

| V <sub>MPP</sub>       | 1.03V - 2.04V         | 2.10V - 2.80V        | 3.20V - 3.5V         |

| t <sub>OFF</sub>       | 0.41μs - 1.39μs       | 1.43µs – 3.80µs      | 6.50µs – 100µs       |

Fig. 10. Simulated  $t_{\text{OFF}}$  for different  $P_{\text{IN}}$  regions.

the on-time generator is triggered to pull  $V_{S2}$  low for a fixed ontime period  $t_{ON}$  of 1  $\mu s$ , turning on the power switch  $S_2$ . After  $t_{ON}$ ,  $V_{S2}$  is pulled high, turning off  $S_2$ . At the same time, the rising edge of  $V_{S2}$  triggers the off-time generator [12] to pull  $V_{S1\_1}$  and  $V_{S1\_2}$  low for turning on  $S_{1\_1}$  and  $S_{1\_2}$ , and it also pulls  $V_{S3}$  high for turning on  $S_3$ . Three switches  $S_{1\_1}$ ,  $S_{1\_2}$ , and  $S_3$  are on for an off-time period  $t_{OFF}$  until  $I_L$  goes to 0, which is detected by the zero-current detector (ZCD). The PFM controller changes CLKDCM based on the  $P_{IN}$  region to minimize the controller's quiescent power. CLKDCM is generated from CLK

Fig. 11. Adaptive digital ZCD. (a) Circuit. (b) Waveform.

Fig. 12. Die micrograph.

by using clock dividers. The SSM controller activates  $S_{1\_2}$  to increase the size of  $S_1$  in the boost mode.

Fig. 9 shows the  $\eta_{CONV}$  improvement in the boost mode by using the proposed control techniques. Fig. 9(a) illustrates an example voltage waveform of  $V_{IN}$  with  $CLK_{DCM}$  when using PSM. To reduce the switching loss, the PSM control skips the switching cycle for two  $CLK_{DCM}$  pulses where  $V_{IN}$  is lower than  $V_{MPP}$ . Although the pulses are skipped, the bandgap reference and the voltage comparator still consume power. To avoid this power loss, PFM can be additionally used [9]. The switching period ( $t_{SW}$ ) is the sum of  $t_{OFF}$  and the time for the current from the PV panel ( $t_{IPV}$ ) to charge the input capacitor  $C_{IN}$ . Fig. 9(b) shows simulated variation of

Fig. 13. Measurement setup.

Fig. 14. Measured waveforms of the overall system operation (a) in the buck mode and (b) in the boost mode.

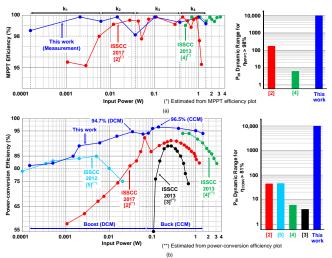

Fig. 15. Measured (a) MPPT and (b) Power-conversion efficiency in comparison with state-of-the-art works.

$t_{SW}$  by  $P_{IN}$  when a fixed  $t_{CLK\_DCM}$  (=  $10~\mu s$ ) is used. In this design,  $CLK_{DCM}$  is generated from CLK:  $t_{CLK\_DCM}=2^n\times t_{CLK}=2^n~\mu s$ . In addition, the period of  $CLK_{DCM}$  ( $t_{CLK\_DCM}$ ) has to be smaller than  $t_{SW}$  to ensure that  $V_{IN}$  can be regulated to  $V_{MPP}.$  Therefore,  $t_{CLK\_DCM}$  for  $k_1,~k_2,$  and  $k_3$  regions are chosen as 64  $\mu s,~32~\mu s,$  and  $128~\mu s,$  respectively.

Since the charged voltage on  $C_F(V_{C\_F})$  ramps up  $I_L$  during  $\Phi_2$ , the peak inductor current  $(I_{L PK})$  can be expressed as follows:

$$I_{L\_PK} = V_{C\_F} \frac{t_{ON}}{L} \tag{1}$$

In the implemented design, a constant on-time ( $t_{ON} = 1 \mu s$ ) is used and L is fixed. Thus,  $I_{L_PK}$  only varies with  $V_{C_LF}$ , which is the subtraction of  $V_{IN}$  from the voltage drop due to the ON-resistance of  $S_1$ . When the size of  $S_1$  increases, the voltage drop decreases, hence increasing  $V_{C_LF}$  as well as  $I_{L_LPK}$ . An increase in  $I_{L_LPK}$  will result in more energy being transferred to the battery improving the efficiency because the energy caused by nonideal ZCD is reduced [9]. The simulated  $\eta_{CONV}$  with a change in the size of  $S_1$  is shown in Fig. 9(c). The power-conversion efficiency is significantly improved at low  $P_{IN}$  levels with a larger size of  $S_1$  while being degraded at high  $P_{IN}$  levels.

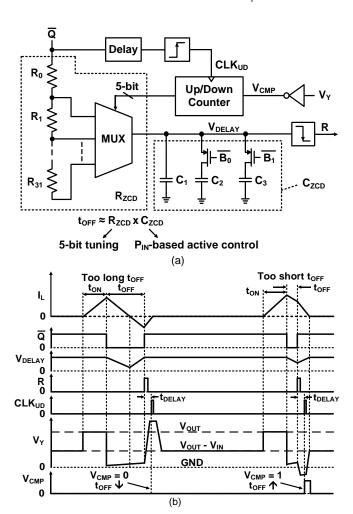

# C. Proposed Adaptive Digital ZCD

An overly long off-time causes power loss due to the reversed inductor current while an overly short off-time dissipates power in the conduction of the body diode and the reverse recovery of the body diode. Thus, an overly long or overly short off-time is likely to result in extra power loss, significantly degrading the power conversion efficiency [13]. Therefore, an accurate ZCD is required to operate the system efficiently, in particular, at low P<sub>IN</sub> levels. The conversion ratio of the hybrid boost mode is the same as that of a simple boost converter [8]. Hence, the off-time can be approximately calculated by the inductor volt-second rule [14] as follows:

$$t_{OFF} = t_{ON} \frac{V_{IN}}{V_{OUT} - V_{IN}} \tag{2}$$

In Eq. (2),  $t_{ON}$  and  $V_{OUT}$  are fixed, and the off-time  $t_{OFF}$  can vary

In Eq. (2),  $t_{ON}$  and  $V_{OUT}$  are fixed, and the off-time  $t_{OFF}$  can vary from hundreds of ns to  $100\mu s$  depending on  $V_{IN}$ , as indicated in Fig. 10. Note that,  $t_{OFF}$  also varies with  $C_{IN}$  due to the change of  $V_{IN}$  deviation from  $V_{MPP}$ . Conventional digital ZCDs with a tunable delay resistor and a fixed delay capacitor [15] that are only applied for a small  $t_{OFF}$  range typically need a large control bit size of over 10 and a long time to reach near-zero  $I_L$  in this wide

range of  $t_{OFF}$ . To address this issue, we propose an adaptive digital ZCD, of which circuit diagram is shown in Fig. 11. The proposed ZCD detects whether  $t_{OFF}$  is overly long or overly short by comparing  $V_Y$  with GND at the end of each off-time period. The comparator output is converted to 5b control by an Up/Down counter. Then,  $t_{OFF}$  is tuned adaptively by only 5b control of the resistor array ( $R_{ZCD}$ ) at every switching cycle to toggle around the ideal value. The capacitor array ( $C_{ZCD}$ ) is adaptively changed based on the  $P_{IN}$  region to adjust  $t_{OFF}$  tuning resolution at the beginning of the sample period. As a result, the settling time of the near-zero inductor current is reduced.

### IV. MEASUREMENT RESULTS

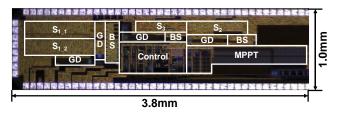

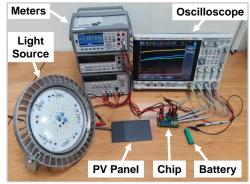

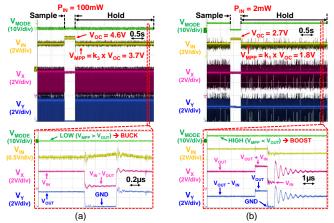

The IC has been fabricated in a 180 nm CMOS process. The die micrograph of the prototype chip is depicted in Fig. 12. The total chip area is 3.8 mm². Fig. 13 shows the measurement setup comprising L = 10 $\mu$ H, C<sub>IN</sub> = C<sub>OUT</sub> = C<sub>F</sub> = 10  $\mu$ F, a 3.5-V 1-cell LiPo battery, and a 1.5-W PV panel. This same setup is also used for the measurements of Fig. 2. The light source for the indoor measurements is a 200-W LED. Fig. 14(a) shows the waveforms at the buck mode measured outdoors at Voc = 4.6 V.

In the hold period, the harvester stays in the CCM with the PWM control to regulate  $V_{\rm IN}$  to  $V_{\rm MPP}$  (= 3.7 V) under the input power of 100 mW. The waveforms at the boost mode measured indoors at  $V_{\rm OC} = 2.7$  V ( $P_{\rm IN} = 2$  mW) are depicted in Fig. 14(b). A proper DCM operation with the PSM control is demonstrated since the resonance exists at the switching node voltages after all the power switches are turned off to enter the idle phase. The operation mode is changed based on  $V_{\rm MODE}$ , which is the comparison result between  $V_{\rm MPP}$  and  $V_{\rm OUT}$ .

Figs. 12(a) and (b) show measured MPPT efficiency  $\eta_{MPPT}$  and power-conversion efficiency  $\eta_{CONV}$  of the proposed PV EH system across a  $10,000 \times P_{IN}$  dynamic range from  $150~\mu W$  to 1.5~W, respectively. As shown in Fig. 15(a), the energy harvester achieves  $>98\%~\eta_{MPPT}$  across the entire  $10,000 \times P_{IN}$  dynamic range with a peak MPPT efficiency of 99.9%. Fig. 15(b) shows that the hybrid buck-boost converter achieves a peak power-conversion efficiency of 96.5%~and maintains an efficiency of more than 81%~across the entire  $P_{IN}$  ranges.

#### V. CONCLUSION

A PV EH system that achieves high MPPT efficiency and high power-conversion efficiency in an ultra-wide dynamic input power range is presented. The proposed MPPT circuit improves the efficiency while consuming a low power of 78 nA. The proposed hybrid buck-boost converter uses only three power switches, achieving high efficiency with small chip area. The IC integrates all the functional blocks in a 3.8 mm × 1 mm die area in a 180nm CMOS process. The proposed EH system is verified by the measurement with a 1.5-W PV panel and a 3.5-V rechargeable battery, providing an energy-effective solution for portable applications.

#### ACKNOWLEDGMENT

This work was supported by the Information Technology Research Center (ITRC) Program (No. IITP-2020-0-01778) through the Institute of Information and Communications Technology Planning and Evaluation (IITP), Korea, funded by the MSIT, Korea. The chip fabrication was supported by the IC Design Education Center(IDEC), Korea.

#### REFERENCES

- [1] J. Jeong, M. Shim, J. Maeng, I. Park, and C. Kim, "An efficiency-aware cooperative multicharger system for photovoltaic energy harvesting achieving 14% efficiency improvement," *IEEE Trans. Power Electron.*, vol. 35, no. 3, pp. 2253–2256, Mar. 2020.

- [2] S. Uprety and H. Lee, "A 0.65-mW-to-1-W photovoltaic energy harvester with irradiance-aware auto-configurable hybrid MPPT achieving> 95% MPPT efficiency and 2.9-ms FOCV transient time," *IEEE J. Solid-State Circuits*, vol. 56, no. 6, pp. 1827–1836, Jun. 2021.

- [3] T.-H. Tsai and K. Chen, "A 3.4 mW photovoltaic energy-harvesting charger with integrated maximum power point tracking and battery management," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 72-73.

- [4] W.-C. Liu, Y.-H. Wang, and T.-H. Kuo, "An adaptive loadline tuning IC for photovoltaic module integrated mobile device with 470μs transient time, over 99% steady-state accuracy and 94% power conversion efficiency," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 70–71.

- [5] K. Kadirvel *et al.*, "A 330 nA energy-harvesting charger with battery management for solar and thermoelectric energy harvesting," in *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*) *Dig. Tech. Papers*, Feb. 2012, pp. 106–108.

- [6] P.-H. Chen, C.-S. Wu, and K.-C. Lin, "A 50 nW-to-10 mW output power tri-mode digital buck converter with self-tracking zero current detection for photovoltaic energy harvesting," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 523–532, Feb. 2016.

- [7] Y. Huh, S.-W. Hong, and G.-H. Cho, "A hybrid structure dual-path step-down converter with 96.2% peak efficiency using 250-mΩ large-DCR inductor," *IEEE J. Solid-State Circuits*, vol. 54, no. 4, pp. 959–967, Apr. 2019.

- [8] Y.-M. Ju et al., "A hybrid inductor-based flying-capacitor-assisted step-up/step-down DC-DC converter with 96.56% efficiency," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 184–185.

- [9] G. Yu, K. W. R. Chew, Z. C. Sun, H. Tang, and L. Siek, "A 400 nW single-inductor dual-input-tri-output DC-DC buck-boost converter with maximum power point tracking for indoor photovoltaic energy harvesting," *IEEE J. Solid-State Circuits*, vol. 50, no. 11, pp. 2758–2772, Nov. 2015.

- [10] S. S. Amin and P. P. Mercier, "MISIMO: A multi-input single-inductor multi-output energy harvesting platform in 28-nm FDSOI for powering net-zero-energy systems," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3407–3419, Dec. 2018.

- [11] D. Schinkel, E. Mensink, E. Kiumperink, E. van Tuijl, and B. Nauta, "A double-tail latch-type voltage sense amplifier with 18 ps setup + hold time," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2007, pp. 314–605.

- [12] Y.-H. Wang, Y.-W. Huang, P.-C. Huang, H.-J. Chen, and T.-H. Kuo, "A single-inductor dual-path three-switch converter with energy recycling technique for light energy harvesting," *IEEE J. Solid-State Circuits*, vol. 51, no. 11, pp. 2716–2728, Nov. 2016.

- [13] T.-C. Huang, C.-Y Hseih, Y.-Y Yang, Y.-H Lee, Y.-C Kang, K.-H. Chen, C.-C Huang, Y.-H Lin, and M.-W. Lee, "A battery-free 217 nw static control power buck converter for wireless RF energy harvesting with α-calibrated dynamic on/off time and adaptive phase lead control," *IEEE J. Solid-State Circuits*, vol. 47, no. 4, pp. 852–862, April. 2012.

- [14] S. Bandyopadhyay and A. P. Chandrakasan, "Platform architecture for solar, thermal and vibration energy combining with MPPT and single inductor," *IEEE J. Solid-State Circuits*, vol. 47, no. 9, pp. 2199–2215, Sep. 2012.

- [15] S. Bandyopadhyay, P. P. Mercier, A. C. Lysaght, K. M. Stankovic, and A. P. Chandrakasan, "A 1.1 nW energy-harvesting system with 544 pW quiescent power for next-generation implants," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 2812–2824, Dec. 2014.

Phan Dang Hung received the B.S. degree from Hanoi University of Science and Technology, Hanoi, Vietnam, in 2017, the M.S. and Ph.D. degrees from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2019 and 2023, respectively. In 2023, he joined Samsung Electronics, Giheung, Korea, as an Analog Circuit Design Engineer.

His research interests include sensor interface, power management, and energy harvesting IC.

Van Thai Trinh received his B.E. degree in Control Engineering and automation from Hanoi University of Science and Technology (HUST), Hanoi, Viet Nam in 2023. Now he is a master's student at the School of Electrical Engineering, Korea Advanced Institute of Science & Technology (KAIST), Daejeon, Korea. His research interests include

sensors, IC (integrated circuit) for energy harvesting, and power management.

Yechan Park received the B.S. degree in electrical engineering from Ajou University, Suwon, South Korea, in 2017, the M.S. and Ph.D. degrees from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2020 and 2025, respectively. His research interests include the design of integrated

circuits and systems for emerging biomedical applications, including wireless power transmission ICs, wireless communication ICs, and power management ICs. Mr. Park was a recipient of the Bronze Prize in the 27th Humantech Paper Award from Samsung Electronics, Suwon, in 2021.

Minkyu Je received the B.S., M.S., and Ph.D. degrees, all in Electrical Engineering, from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1996, 1998, and 2003, respectively.

In 2003, he joined Samsung Electronics, Giheung, Korea, as a Senior Engineer and worked on multi-mode multi-band RF transceiver SoCs for

GSM/GPRS/EDGE/WCDMA standards. From 2006 to 2013, he was with Institute of Microelectronics (IME), Agency for Science, Technology and Research (A\*STAR), Singapore. He worked as a Senior Research Engineer from 2006 to 2007, a Member of Technical Staff from 2008 to 2011, a Senior Scientist in 2012, and a Deputy Director in 2013. From 2011

to 2013, he led the Integrated Circuits and Systems Laboratory at IME as a Department Head. In IME, he led various projects developing low-power 3D accelerometer ASICs for high-end medical motion sensing applications, readout ASICs for nanowire biosensor arrays detecting DNA/RNA and protein biomarkers for point-of-care diagnostics, ultra-low-power sensor node SoCs for continuous real-time wireless health monitoring, and wireless implantable sensor ASICs for medical devices, as well as low-power radio SoCs and MEMS interface/control SoCs for consumer electronics and industrial applications. He was also a Program Director of NeuroDevices Program under A\*STAR Science and Engineering Research Council (SERC) from 2011 to 2013, and an Adjunct Assistant Professor in the Department of Electrical and Computer Engineering at National University of Singapore (NUS) from 2010 to 2013. He was an Associate Professor in the Department of Information and Communication Engineering at Daegu Gyenogbuk Institute of Science and Technology (DGIST), Korea from 2014 to 2015. Since 2016, he has been an Associate Professor in the School of Electrical Engineering at Korea Advanced Institute of Science and Technology (KAIST), Korea.

His main research areas are advanced IC platform development including smart sensor interface ICs and ultralow-power wireless communication ICs, as well as microsystem integration leveraging the advanced IC platform for emerging applications such as intelligent miniature biomedical devices, ubiquitous wireless sensor nodes, and future mobile devices. He is an editor of 1 book, an author of 6 book chapters, and has more than 300 peer-reviewed international conference and journal publications in the areas of sensor interface IC, wireless IC, biomedical microsystem, 3D IC, device modeling, and nanoelectronics. He also has more than 50 patents issued or filed. He has served on the Technical Program Committee and Organizing Committee for various international conferences, symposiums, and workshops, including IEEE International Solid-State Circuits Conference (ISSCC), IEEE Asian Solid-State Circuits Conference (A-SSCC), and IEEE Symposium on VLSI Circuits (SOVC). He is currently working as a Distinguished Lecturer of IEEE Circuits and Systems Society.