# D-band High Gain and Wide Bandwidth Power Amplifier Design in 65nm CMOS Adopting Dual-Peak $G_{\text{max}}$ Technique

### Hyo-Ryeong Jeon<sup>1</sup> and Sang-Gug Lee<sup>(a)</sup>

Department of Electrical Engineering, Korea Advanced Institute of Science and Technology E-mail: ¹gyfud0929@kaist.ac.kr

Abstract – This paper presents a design of a CMOS D-band high gain and wide bandwidth amplifier adopting the dualpeak  $G_{\rm max}$  technique. The proposed amplifier applies the dualfrequency  $G_{\rm max}$  technique based on 3-embedding, which provides high gain over a wide bandwidth. By utilizing the degree of freedom of 3-embedding, we designed a core with optimal input and output impedance. After that, a D-band 3-stage power amplifier is constructed using the designed  $G_{\rm max}$ -core. When VDD=1V, the measured gain peaks 16.8 dB at 161 GHz with the 3-dB bandwidth of 18.6 GHz and the operating frequency from 150.2 GHz to 168.8 GHz. The maximum output power is 5.65 dBm at 159 GHz and shows performance ranging from 1.39 to 5.65 dBm across the entire operating frequency range. The DC power consumption is 98 mW. The total chip area of the power amplifier is 0.224 mm².

Keywords—CMOS, D-band, PA, gain boosting, wideband

#### I. INTRODUCTION

In recent years, sub-terahertz systems have been attractive in various applications such as high-speed data communication, spectroscopy, and radar. Among the sub-terahertz frequency bands, the D-band (110-170GHz) is a promising frequency band for 6G communication. Therefore, low-cost and high-density D-band systems using CMOS technology have been extensively studied.

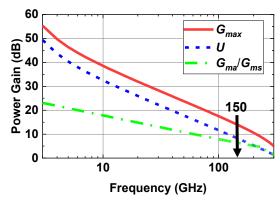

However, the intrinsic gain of transistors is low in the D-band. As shown in Fig. 1, for a 65nm CMOS, a 28um transistor has a  $G_{ma}/G_{ms}$  of 6 dB and a unilateral gain (U) of 8 dB. Low intrinsic gain results in increased transistors to implement the high gain amplifier, consuming a lot of power and area.

To solve this problem, the concept of  $G_{\rm max}$ , which refers to the theoretical maximum gain of a transistor, was proposed in [1] and implemented through an embedding network. As shown in Fig. 1, a 28um transistor in a 65nm CMOS has a  $G_{\rm max}$  of 13.6 dB at 150 GHz, which theoretically allows for implementing an amplifier with a gain per stage that is 5.6 dB higher than U. Subsequently, in [2], a degree of freedom was added to the  $G_{\rm max}$ -core design by constructing a 3-component  $G_{\rm max}$ -core, which allowed for the free adjustment of input/output impedance for optimized matching. However,

a. Corresponding author; sgjlee@kaist.ac.kr

Manuscript Received Mar. 14, 2023, Revised Jun. 12, 2023, Accepted Jun. 19, 2023

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<a href="http://creativecommons.org/licenses/by-nc/4.0">http://creativecommons.org/licenses/by-nc/4.0</a>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Fig. 1. Simulated gain performances of a 28um transistor for a 65nm CMOS

the  $G_{\rm max}$ -core has a narrow bandwidth despite having a high gain. To overcome this limitation, [3] proposed the dual-peak Gmax technology, which can have a wide and high gain in the frequency range between two frequencies where the  $G_{\rm max}$  condition is satisfied.

In this article, we demonstrate the design of a high gain and wide bandwidth D-band power amplifier adopting the dual-peak  $G_{\rm max}$  technique. Moreover, through load-pull simulation, we found a combination of components among the countless combinations of 3-component elements that can achieve output gain matching and power matching simultaneously at the operating frequency, enabling high gain and high output power simultaneously. Section II describes the design methodology of the Dual-peak  $G_{\rm max}$ -core and 3-stage D-band power amplifier. Section III presents the simulation results of the designed power amplifier and concludes in Section IV.

### II. DESIGN METHODOLOGY

A. Dual-peak G<sub>max</sub>-Core with 3-component embedding network

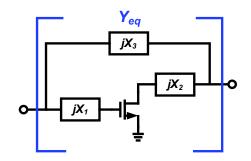

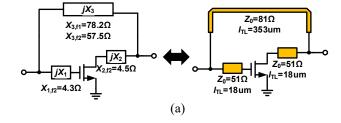

Fig. 2 shows the block diagram of a three-component-based  $G_{\text{max}}$ -core. By adjusting the values of the three components to satisfy a  $G_{\text{max}}$  condition [2]:

$$Y_{21,eq}/Y_{12,eq} = -G_{max},$$

(1)

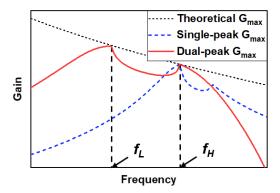

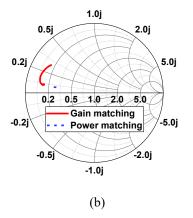

the transistor can achieve a gain equivalent to  $G_{\text{max}}$ . If (1) is met at only one frequency, it is called a single-peak  $G_{\text{max}}$ , and if (1) is satisfied at two frequencies simultaneously, it is called a dual-peak  $G_{\text{max}}$ . As shown in Fig. 3, the dual-peak

Fig. 2. A block diagram of a 3-component-based  $G_{\text{max}}$ -core

Fig. 3. A comparison of single-peak  $G_{\text{max}}$  and dual-peak  $G_{\text{max}}$

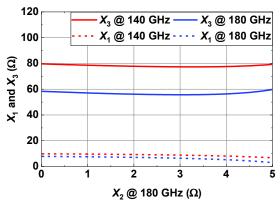

Fig. 4.  $X_1$  and  $X_3$  versus  $X_2$  required to achieve  $G_{\rm max}$ -condition with a 28um transistor in 65nm CMOS at 140 and 180GHz

$G_{\rm max}$  has a high gain close to  $G_{\rm max}$  over a wide frequency range between the peak frequencies. Therefore, by using a dual-peak  $G_{\rm max}$ -core, a broadband amplifier can be easily implemented.

Fig. 4 shows  $X_1$  and  $X_3$  versus  $X_2$  required to achieve  $G_{\rm max}$  condition with a 28um transistor in 65nm CMOS at 140 and 180 GHz. The transistor size is determined considering the gain and output power properties. As shown in Fig. 4, an infinite number of combinations of  $X_1, X_2$ , and  $X_3$  can be used to implement the  $G_{\rm max}$ -core with three components. However, since the input and output impedance of the  $G_{\rm max}$ -core changes depending on the combination, it is common to choose a combination that optimizes input and output impedance matching [2].

Fig. 5. (a) Design details of the  $G_{\rm max}$ -core that satisfies the  $G_{\rm max}$  condition at 140 and 180 GHz and (b) simulated output power and gain matching impedance of designed  $G_{\rm max}$ -core from 140 to 180 GHz.

## B. 3-stage D-band Dual-peak $G_{max}$ -based Power Amplifier Design

Fig. 5 (a) shows the design details of the core that satisfies the  $G_{\text{max}}$  condition at 140 and 180 GHz. The values of the three components,  $X_1, X_2$ , and  $X_3$ , are chosen from the infinite combinations in Fig. 4 to align the output small-signal gain matching and output power matching. In this design, transmission lines (TLs) are used to implement the required reactance values based on the equation [2]:

$$X_{\rm eq} = Z_0 \sin(\beta l_{TL}) \tag{2}$$

where  $Z_0$  is a characteristic impedance of the transmission line,  $\beta$  and  $I_{\text{TL}}$  are the beta and length of the transmission line, respectively.  $X_3$ , which has a smaller value at high frequencies, can be implemented with a transmission line of a length of lambda/4 or longer [3]. The actual value of the parameters of the TL differs from the calculated value by approximately 5-10% due to losses and couplings in the actual TL. Fig. 5 (b) is the simulated output power and gain matching impedance of the designed  $G_{\text{max}}$ -core from 140 to 180 GHz. This core chose a combination with a closely located output gain matching and power matching. By designing an amplifier with this proposed  $G_{\text{max}}$ -core, output power matching can be achieved without small-signal gain degradation. Therefore, achieving a wide, flat, and high gain and output power is accessible.

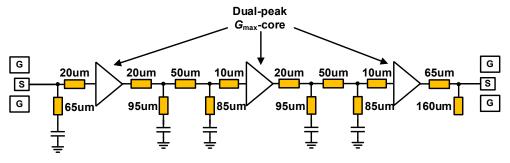

Fig. 6 shows the circuit schematic of the 3-stage D-band dual-peak  $G_{\rm max}$ -based amplifier.  $G_{\rm max}$ -core, shown in Fig. 5, constitutes each stage, and the inter-stage matching networks are simultaneously input and output matched over a wide bandwidth using transmission lines. The input and output

Fig. 6. A circuit schematic of the 3-stage D-band dual-peak  $G_{\text{max}}$ -based power amplifier

Fig. 7. Design procedure of a dual-peak  $G_{\text{max}}$ -based power amplifier.

impedance is also broadband matched to 50ohm source and load impedance using transmission lines.

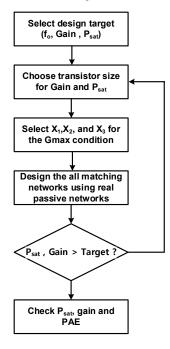

Fig. 7 represents the dual-peak  $G_{\text{max}}$ -based amplifier design procedure. The optimal transistor size is determined by considering the desired power gain and the output power (or saturated output power,  $P_{\text{sat}}$ ). The  $X_1$ ,  $X_2$ , and  $X_3$  are selected the  $G_{\text{max}}$ -condition at two frequencies.  $X_1, X_2$ , and  $X_3$  are determined from infinite combinations to meet the required objective, e.g., output power and gain simultaneous matching. After selecting the specific  $X_1$ ,  $X_2$ , and  $X_3$  values, implement each with a passive component like a transmission line or cap. The matching networks are also designed with passive components. EM simulation tools such as HFSS or EMX can simulate and verify all passive networks. After the amplifier implementation, check the overall performances, such as power gain,  $P_{\text{sat}}$ , and power added efficiency (PAE).

### III. RESULTS AND DISCUSSIONS

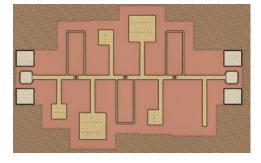

Fig. 8 shows the chip micrograph of the designed 3-stage D-band dual-peak  $G_{\rm max}$ -core-based power amplifier. The chip dimensions, including the pads, are 0.77mm x 0.423mm, while the core size without the pad is 0.529mm x 0.423mm.

Fig. 8. Chip micrograph of designed 3-stage D-band dual-peak  $G_{\max}$ -core based power amplifier

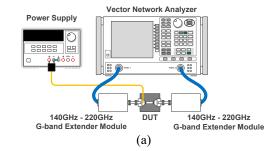

Fig. 9. Measurement set-ups at G-band. (a) S-parameter measurement and (b) power measurement

This chip is located on a PCB to measure by on-wafer probing. Fig. 9 shows the measurement set-ups at G-band. The S-parameter measurement uses the G-band extension modules (V05VNA2 Series WR05) and a vector network analyzer (N5247A PNA-X). The power measurement uses a signal generator (N5173B) with a D-band extension module (WR6.5SGX) and a power meter (PM5) for the input power source and the output power measurement, respectively. DC bias voltage enters through the input and output probes.

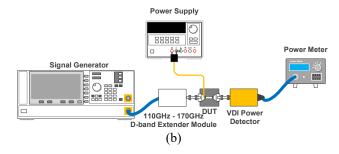

Fig. 10 shows the measurement results with VDD=1V compared to simulation results. The gain peaks 16.8 dB at 161 GHz with the 3-dB bandwidth of 18.6 GHz and the

Fig. 10. Measurement results of 3-stage D-band dual-peak  $G_{\text{max}}$ -based power amplifier: (a) S-parameters, (b) k-factor  $(k_{\text{f}})$ ,  $|\Delta|$ , and (c)  $P_{\text{sat}}$ .

operating frequency from 150.2 GHz to 168.8 GHz. Stability is maintained stable across the entire operating frequency range. The maximum output power is 5.65 dBm at 159 GHz and shows performance ranging from 1.39 to 5.65 dBm across the entire operating frequency range. Compared to the simulation results, the peak gain decreased by 3.1 dB, the bandwidth decreased by 22 GHz, and the maximum output power decreased by 0.46 dBm while dissipating 98 mW PDC. This discrepancy is due to the influence of uncalculated parasitic components caused by inaccuracies in the transistor modeling at high frequencies. The performance is summarized in Table I with a comparison to state-of-theart. The proposed amplifier achieves state-of-the-art levels of gain, bandwidth, and  $P_{\rm sat}$ .

TABLE I. Performance Summary in Comparison with State-Of-The-Art

|                            | This work    | [4]          | [5]          | [6]          |

|----------------------------|--------------|--------------|--------------|--------------|

| Tech.                      | 65nm<br>CMOS | 65nm<br>CMOS | 45nm<br>CMOS | 28nm<br>CMOS |

| Gain<br>(dB)               | 16.8         | 17.5         | 16           | 14.3         |

| f <sub>0</sub><br>(GHz)    | 159.5        | 150          | 141          | 190          |

| BW <sub>3dB</sub><br>(GHz) | 18.6         | 5            | 31.5         | 14.4         |

| P <sub>sat</sub><br>(dBm)  | 5.65         | 10.4         | 5.4          | 1.5          |

| P <sub>DC</sub> (mW)       | 98           | 86.3         | 75           | 45           |

| Core Area (mm²)            | 0.224        | 0.16         | 0.072        | 0.09         |

### IV. CONCLUSION

We proposed a D-band 3-stage power amplifier with high gain and wide bandwidth in this work. A  $G_{\rm max}$ -core with a wide operating frequency range of 140-180 GHz is constructed using the dual-peak  $G_{\rm max}$  technique. Moreover, the degrees of freedom of the 3-component-based  $G_{\rm max}$ -core make the small-signal output gain matching and large-signal output power matching of the  $G_{\rm max}$ -core close, enabling high gain and high output power simultaneously. By using this  $G_{\rm max}$ -core as gain stages, the designed power amplifier achieved a measured peak gain of 16.8 dB and a 3-dB bandwidth of 18.6 GHz with a maximum output power of 5.65 dBm, using DC power of 98 mW when VDD=1V.

### ACKNOWLEDGMENT

The chip fabrication was supported by the IC Design Education Center (IDEC), Korea.

### REFERENCES

- [1] H. Bameri and O. Momeni, "A High-Gain mm-Wave Amplifier Design: An Analytical Approach to Power Gain Boosting," in IEEE Journal of Solid-State Circuits, vol. 52, no. 2, pp. 357-370, Feb. 2017.

- [2] D. -W. Park, D. R. Utomo, B. H. Lam, J. -P. Hong and S. -G. Lee, "A 280-/300-GHz Three-Stage Amplifiers in 65-nm CMOS With 12-/9-dB Gain and 1.6/1.4% PAE While Dissipating 17.9 mW," in IEEE Microwave and Wireless Components Letters, vol. 28, no. 1, pp. 79-81, Jan. 2018.

- [3] D. -W. Park, D. R. Utomo, B. H. Lam, S. -G. Lee and J. -P. Hong, "A 230–260-GHz Wideband and High-Gain Amplifier in 65-nm CMOS Based on Dual-Peak G<sub>max</sub> Core," in IEEE Journal of Solid-State Circuits, vol. 54, no. 6, pp. 1613-1623, June 2019.

- [4] D.-W. Park, D. R. Utomo, B. Yun, H. U. Mahmood, and S.-G. Lee, "A D-band power amplifier in 65-nm CMOS by adopting simultaneous output power-and gain-atched *G*<sub>max</sub>-core," IEEE Access, vol. 9, pp. 99 039–99 049, 2021.

- [5] A. Hamani, A. Siligaris, B. Blampey, C. Dehos, and J. L.

- Gonza-lez Jimenez, "A 125.5-157 GHz 8 dB NF and 16 db of gain D-band low noise amplifier in CMOS SOI 45 nm," in 2020 IEEE/MTT-S International Microwave Symposium (IMS), 2020, pp. 197–200.

- [6] D. Simic and P. Reynaert, "Analysis and design of lossy capacitive over-neutralization technique for amplifiers operating near fmax," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 5, pp. 1945–1955, 2021.

Hyo-ryeong Jeon received the B.S. and M.S. degrees in electrical engineering from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 2020 and 2022, respectively, where he is currently pursuing the Ph.D. degree in electrical and electronic engineering. His current research interests include sub-THz, mm-

wave, and RF-integrated circuits based on CMOS technology.

Sang-Gug Lee received his B.S. degree in electronic engineering from Kyungpook National University, Daegu, South Korea, in 1981, and the M.S. and Ph.D. degrees in electrical engineering from the University of Florida, Gainesville, FL, USA, in 1989 and 1992, respectively. In 1992, he joined Harris Semiconductor, Melbourne, FL, USA, where he was

involved in silicon-based radio frequency (RF) integrated circuit designs. From 1995 to 1998, he was an Assistant Professor with the School of Computer and Electrical Engineering, Handong University, Pohang, South Korea. From 1998 to 2009, he was a Professor with the Information and Communications University, Daejeon, South Korea. Since 2009, he has been a Professor with the Department of Electrical Engineering, Korea Advanced Institute of Science and Technology (KAIST), Daejeon. He served as the Research Director for the Auto-ID Laboratory KAIST, from 2005 to 2010. In 2007, his laboratory was selected as a National Research Laboratory. Since 2012, he has been serving as the Director for the Future Promising Fusion Technology Pioneer Center, leading a research group in silicon-technology-based terahertz integrated circuit (IC) design. His current research interests include CMOS-based radio frequency (RF), analog, and mixed-mode IC designs for various radio transceiver applications, low-power transceivers, extreme high-frequency (terahertz) circuit design based on CMOS technology, and other analog integrated circuit designs such as display semiconductors, power management ICs, and automotive ICs. He has also served as a Technical Committee member for IEEE ISSCC of the Wireless Communication Technology Committee from 2005 to 2009.