# Design of an H-band Frequency Tripler and Buffer Amplifier IC in 250-nm InP HBT Process

Hyung Eun Kim<sup>1</sup>, Yeong Min Jang, Yeong Chae Jeon and Jin Ho Jeong<sup>a</sup>

Department of Electronic Engineering, Sogang University

E-mail : <sup>1</sup>lcksasin9@sogang.ac.kr

**Abstract –** In this paper, we propose the design of an H-band(220-330 GHz) frequency tripler, buffer amplifier IC(Integrated Circuit) using 250-nm InP HBT technologies. H-band frequency tripler is designed by using triple-push technique and is composed of 3-way 120° power divider and coupled line. Simulated result of H-band tripler shows -3 dBm output power while measured result shows between -9 and -6 dBm output power. Spectrum result of H-band tripler is down-converted by H-band harmonic mixer but it shows H-band tripler operates well at H-band. To decrease buffer amplifier chip area, we use cascode method in buffer amplifier design. IC with H-band tripler and buffer shows 5.6 dBm output power and -3.6 dB conversion gain. Finally, to decrease performance degradation due to off-chip transition, we will design on-chip transition connecting waveguide and microstrip.

**Keywords—** Buffer amplifier, H-band, Millimeter wave, Tripler

## I. INTRODUCTION

THz frequency band, over 100 GHz, can be widely used for commercial or military purpose such as next 6G communication, security scan. For small THz circuit design that has low price, we need THz signal source based on transistor IC. Frequency multiplier and amplifier is core block of this IC.

As CMOS process based on Silicon is limited in output power at THz band, compound semiconductor such as SiGe, GaAs, GaN, InP is widely used instead of CMOS process. However, output power that can be obtained by one stage amplifier circuit is limited (inversely proportional to square of frequency). Also, existence of parasitic component of circuit leads to poor performance at THz band.

In H-band, frequency multiplier is widely used to generate signal in compound semiconductor process [1,2]. Conventional designed frequency multiplier has large chip area or shows low power and gain according to order of multiplier [3,4].

So, in this paper, we present high order frequency multiplier technique to increase power and conversion gain

a. Corresponding author; jjeong@sogang.ac.kr

Manuscript Received Mar. 28, 2022, Accepted Sep. 10, 2022

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<http://creativecommons.org/licenses/by-nc/3.0>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

of tripler. Also, we design buffer amplifier to increase output power and gain. Finally, we will design on-chip transition to decrease out-chip packaging area in 250-nm InP HBT technology. Through this process, we minimize off-chip circuit and packaging and it leads to small THz signal source that has low price and good performance.

## II. CIRCUIT DESIGN

### A. 250-nm InP HBT technology

For generating high frequency signal such as terahertz bands, high-order frequency multiplier is advantageous. However, as order of multiplier increases, gain of power of frequency multiplier becomes low because of non-linearity of transistor. So, in this paper, we used W-band (75-110 GHz) to generate H-band frequency signal.

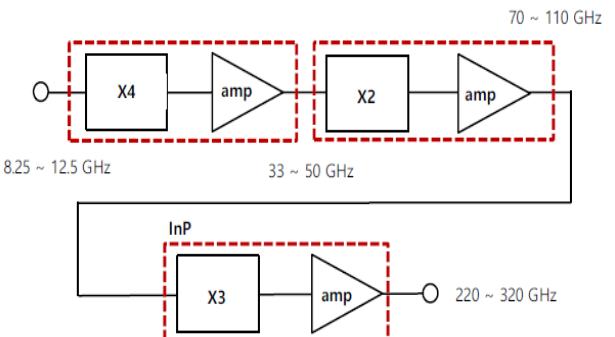

Fig. 1 shows block diagram for H-band signal generation. We designed IC with H-band tripler and buffer amplifier in 250-nm InP HBT process.

Fig. 1. THz signal generation using frequency multiplier, amplifier

In THZ frequency band, to check IC operate well, Full-wave electromagnetic (EM) simulations were performed to design all composed circuits. EM simulations were carried out using Advanced Design System (ADS) momentum from Keysight Technologies. As this simulated results shows parasitic component of transistor, we design IC considering that parasitic effect.

250-nm InP HBT technologies is composed of 4 metal layer(M1~M4). IC is designed on the bottom metal (M1) considering small metallic loss. And metal (M3) is used as ground metal.

## B. Design of H-band Frequency Tripler

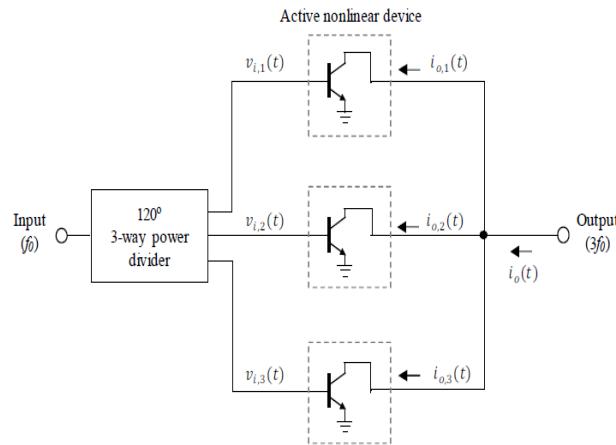

H-band frequency tripler used triple-push method and it is shown as Fig. 2 [5]. 3-way-120° power divider is core block of H-band frequency tripler and it is composed of 2 Lang couplers that has different power ratio and 30° phase delay lines. Output signal power from 3-way 120° power divider has 120° phase difference at fundamental frequency (sum of phase delay line and Lang coupler) and same magnitude.

At  $n$ th harmonic component, phase of output signal from power divider increases  $n$  times larger than fundamental case. Then, at fundamental, 2nd harmonic component, total output power decreased because of offset between  $i_{o,2}(t)$  and  $i_{o,3}(t)$  and total output power decreased. While, at 3rd harmonic frequency, phase of  $i_{o,1}(t)$ ,  $i_{o,2}(t)$  and  $i_{o,3}(t)$  is same. So, total output power at 3rd harmonic frequency increased and we generate H-band signal using W-band signal.

Fig. 2. Frequency tripler topology using triple-push method

The designed power divider has almost equal power division difference between three output ports, with good return loss at the center frequency around 90 GHz. Simulated result of power divider shows that return loss of output ports was better than -14 dB and insertion loss of output ports was better than -8 dB in the entire W-band.

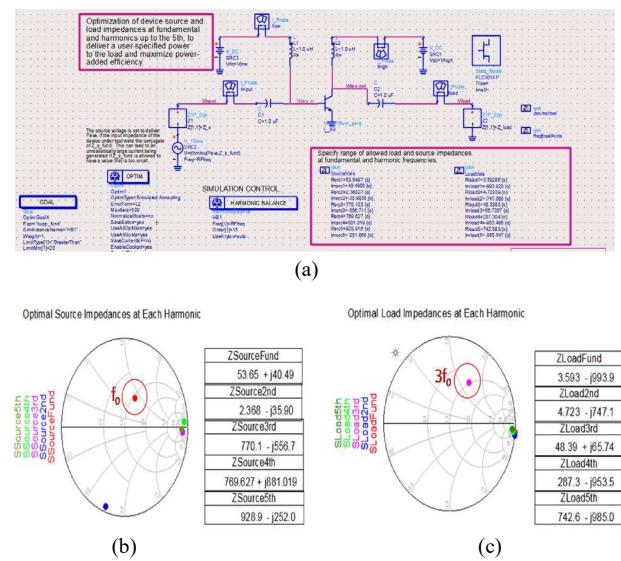

Output power of H-band tripler is generally very small value, because of harmonic component. So, impedance matching at harmonic frequency to increase output power is important. To design output power of harmonic component, consideration of accurate transistor model is necessary. In response to these problems, we need to check full-wave EM simulation results of total IC. Fig. 3(a) illustrates harmonic load-pull simulation setup in ADS. Using this setup leads to optimized impedance (that makes maximum output power and maximum conversion gain) at harmonic frequency including fundamental frequency case. Fig. 3(b) ~ 3(c) shows the contour of optimized impedance at fundamental frequency and 3rd harmonic frequency. Considering this optimized impedance contour, we decided the most optimized impedance for H-band tripler.

Fig. 3. Harmonic load-pull simulation (a) setup (b) contour at fundamental frequency (c) contour at 3rd harmonic

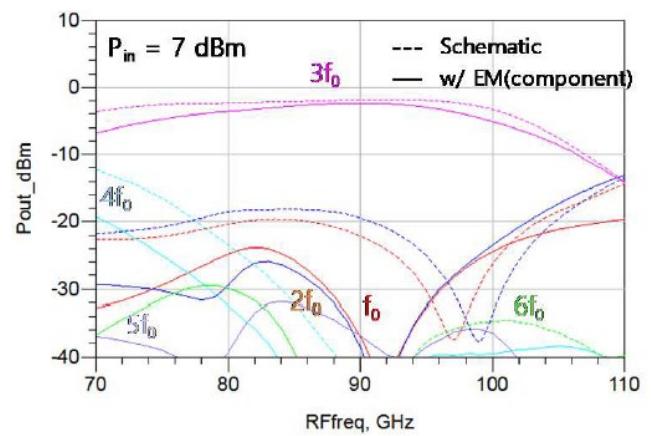

At high frequency band, loss from parasitic effect increases and parasitic component also increases. To design circuit precisely at high frequency band, we need to consider parasitic effect of circuit. So, we used full-wave EM simulation data for circuit design. In circuit simulation, we replace circuit design such as 3-way 120° power divider, interconnection lines to EM data. Fig. 4 shows simulated results with EM data. At fundamental and other harmonic frequency, the difference between EM data and schematic data is much larger than 3rd harmonic case and that value is very low. So, designed H-band tripler with EM data works better than schematic case. In practice, output power of 3rd harmonic component is about -8 ~ -4 dBm between 70 ~ 100 GHz while output power at each harmonic frequency has lower value than -18 dBm.

Fig. 4. Simulated output power with EM at each harmonic frequency

After harmonic load-pull simulation and EM analysis, input and output impedance matching network of H-band tripler is optimized. We can obtain high output power at 3rd harmonic frequency while fundamental and 2nd harmonic component is small value. Designed tripler is simulated when  $f_0$  is 90 GHz or input power is 3.5 dBm.

When  $f_0$  is fixed to 90 GHz, conversion gain of 3rd harmonic component is -10.2 dB where the input power is 3.5 dBm. However, at fundamental and 2nd harmonic case, conversion gain is lower than -30 dB.

When input power is fixed to 3.5 dBm, output power of 3rd harmonic component is greater than -15 dBm in W-band. However, at fundamental and 2nd harmonic case, output power is also lower than -15 dBm in W-band. So, H-band tripler shows wideband performance at 3rd harmonic frequency.

### C. Design of H-band buffer amplifier

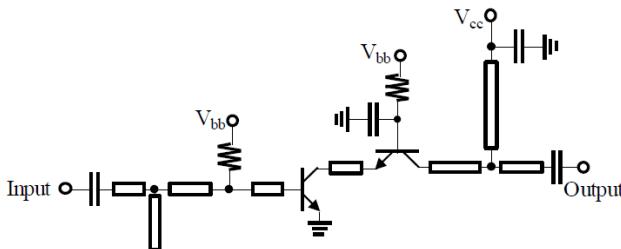

H-band tripler has high output power at 3rd harmonic frequency. However, it is relative high value comparing fundamental and 2nd harmonic component. We need to amplify output of tripler to use signal source. So, to amplify high output power, we design H-band buffer amplifier [6]. As H-band is also high frequency, chip area becomes larger than lower frequency band. To decrease chip area, we design transistor with cascode method, as illustrated in Fig. 5. Cascode method use CE, CB type amplifier circuit. By cascode method, we connected emitter of CB type amplifier circuit and collector of CE type amplifier circuit. In circuit design, H-band amplifier is differential mode, balun is used at input port and output port of power amplifier [6].

Fig. 5. H-band buffer amplifier topology with cascode method

### III. RESULTS AND DISCUSSION

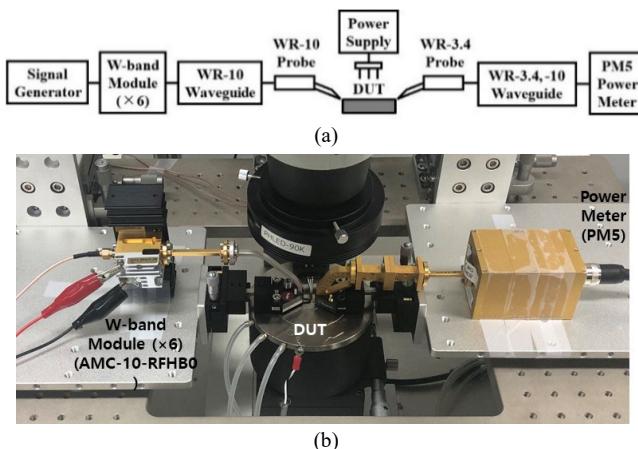

As module design is in process, designed IC circuits is measured by on-wafer probing, as illustrated in Fig. 6. Fig. 6 is for power measurement. In power measurement setup, using W-band module, measured results by power meter is H-band signal. When measuring the power value, loss of waveguide needs to be considered.

Fig. 6. Measurement setup for power measurement; (a) block diagram (b) Photograph

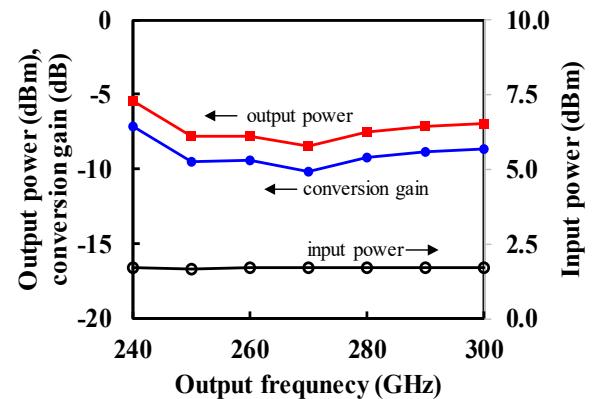

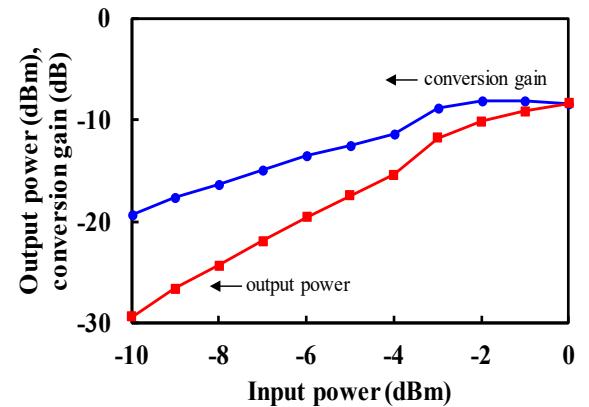

As shown in Fig. 7, we measured output power and conversion gain of H-band tripler when input power is around 1.7 dBm. Measured output power was between -9 dBm and -5.0 dBm at 240~300 GHz. Measured conversion gain was between -7 dB and -10 dB. Fig. 8 shows conversion gain and output power of H-band tripler when  $f_0$  is 90 GHz. Maximum conversion gain shows about -9~10 dB and output power is about -9~10 dBm where input power is 0 dBm.

Fig. 7. Measured output power and conversion gain of the frequency tripler at input power around 1.7 dBm

Fig. 8. Measured output power and conversion gain of the frequency tripler at frequency around 270 GHz

In high frequency band, off-chip process degrades performance because of parasitic component. So, we would design on-chip transition to decrease parasitic loss. After design of on-chip transition, IC and on-chip transition will be combined to module. When module is completely built, we can measure power of module with IC, on-chip transition [7]. It is similar power measurement setup by power meter same as Fig. 6. In Fig. 6, on-wafer probe is replaced to on-chip transition. So, it is more convenient in measurement using waveguide and protect performance degradation.

### IV. CONCLUSION

In this paper, we designed H-band IC with frequency tripler and buffer amplifier in 250-nm InP HBT technology.

All IC circuit is designed using EM simulation by ADS. Triple-push technique is used to generate H-band signal and cascode method is used to decrease chip area while satisfying output power conditions. Thus, designed H-band IC shows good performance in H-band.

Simulated results of tripler shows -3 dBm at H-band. Measured output power of H-band tripler exhibited about -9 dBm where input power is around 1.7 dBm and exhibited about -9 dBm where frequency is 270 GHz. Also, it shows wideband performance (about -6~10 dB) in 240-300 GHz. So, it shows that to make H-band signal source using H-band tripler and buffer amplifier was almost completed. From now on, we need to improve performance of IC and design on-chip transition. The designed IC and on-chip transition are fabricated using 250-nm InP HBT technology.

#### V. ACKNOWLEDGMENT

The authors would like to thank IDEC for the design tool and process supports.

#### REFERENCES

- [1] Ojefors. E, Heinemann. B and Pfeiffer. U.R, "A 325 GHz Frequency Multiplier Chain in a SiGe HBT Technology," in *Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium*, Anaheim, CA, USA, 23-25 May 2010; pp. 91-94.

- [2] Grottsch. C.M. Wagner. S. Leuther. A, Meier. D, and Kallfass. I, "Ultra-Broadband Frequency Multiplier MMICs for Communication and Radar Applications," in *Proceedings of the 13th European Microwave Integrated Circuits Conference*, Madrid, Spain, 23-25 Sep. 2018; pp. 113-116

- [3] Lewark. U.J, Tessman. A, Wagner. S, Leuther. A, Zwick. T, Kallfass, I, "255 TO 330 GHz Active Frequency Tripler MMIC," in *Proceedings of the Integrated Nonlinear Microwave and Millimeter-wave Circuits*, Dublin, Ireland, 3-4 Sep. 2012; pp. 1-3.

- [4] Lin. H.C, Rebeiz. G.M, "A 200-245 GHz Balanced Frequency Doubler with Peak Output Power of +2 dBm," in *Proceedings of the IEEE Compound Semiconductor Integrated Circuit Symposium*, Monterey, CA, USA, 13-16 Oct. 2013; pp. 1-4.

- [5] J. Jeong, J. Choi, J. Kim, W. Choe, "H-Band InP HBT Frequency Tripler Using the Tripler-Push Technique" *Electronics*, vol. 9. no. 12, pp. 1-7, Dec., 2020.

- [6] J. Kim, S. Jeon, M. Kim, M. Urtega, J. Jeong, "H-band Power Amplifier Integrated Circuits Using 250-nm InP HBT Technology," *IEEE Transactions on Terahertz Science and Technology*, vol. 5. no. 2, pp. 215-222, Mar. 2015

- [7] K. M. K. H. Leong et al., "A 340-380 GHz integrated CB-CPW-to-waveguide transition for sub millimeter-wave MMIC Packaging," *IEEE Microwave and Wireless Components. Letters*, vol. 19, no. 6, pp. 413-415, Jun. 2009

**Hyung Eun Kim** received the B.S. degree in electronic engineering from Sogang University, Seoul, South Korea, in 2020. He is currently working toward the Ph.D. degree in electronic engineering at Sogang University, Seoul.

His research interest includes High speed circuits, oscillators, and THz integrated circuits.

**Yeong Min Jang** received the B.S. degree in electrical engineering from Donga University, Busan, South Korea, in 2020. He is currently working toward the Ph.D. degree in electronic engineering at Sogang University, Seoul.

His research interest includes monolithic microwave integrated circuits, THz integrated circuits, and

wireless power amplifier.

**Yeong Chae Jeon** received the B.S. degree in electrical engineering from Donga University, Busan, South Korea, in 2021. He is currently working toward the Ms. degree in electronic engineering at Sogang University, Seoul.

His research interest includes THz integrated circuits module and packaging, millimeter wave passive

**Jin Ho Jeong** received the B.S., M.S., and Ph.D. degrees in electrical engineering from Seoul National University, Seoul, South Korea, in 1997, 1999, and 2004, respectively. From 2004 to 2007, he was in the University of California at San Diego, La Jolla, CA, USA, as a Postdoctoral Scholar, where he was involved with the design of high efficiency and high-linearity RF power amplifiers. In 2007, he joined the Department of Electronics and Communications Engineering, Kwangwoon University, Seoul. Since 2010, he has been with the Department of Electronic Engineering, Sogang University, Seoul. His research interests include monolithic microwave integrated circuits, THz integrated circuits, high-efficiency/high-linearity power amplifiers and oscillators, and wireless power transfers