# Fully Integrated Triple-Mode Ka-Band Power Amplifier with Vertical-Horizontal Combined Transformer for 5G NR Applications

# Geun Tae Kim<sup>1</sup>, Kyu Taek Oh, Hyun Jin Ahn<sup>2</sup> and Ock Goo Lee<sup>a</sup>

<sup>1,a</sup>Department of Electrical Engineering, Pusan National University

<sup>2</sup>Qualcomm Inc., San Diego, CA, USA

E-mail: <sup>1</sup>sclan32@pusan.ac.kr

Abstract – This paper presents a fully integrated triple-mode Ka-band power amplifier with a vertical-horizontal combined transformer for 5G NR applications, in 65 nm bulk CMOS process. With discrete power control using the proposed vertical-horizontal combined transformer, the triple-mode PA achieves enhanced efficiency performance in the power back-off region. The fully integrated triple-mode PA achieves 18.4-, 21.9-, and 23.5-dBm saturated output powers with 27.2, 34.9, and 41.5% peak PAEs in low power (LP), middle power (MP), and high power (HP) modes, respectively. The triple-mode PA can reduce the current consumption in LP the and MP modes.

# *Keywords*—5G, High Efficiency, Power amplifier (PA), Power combiner, Triple-mode control

# I. INTRODUCTION

With the increasing demand for large amounts of data communication, more efforts have been made for 5G new radio (NR) wireless communications. Additionally, several studies on the integration of 5G mm-wave transceivers have been actively studied [1]-[18]. Most 5G mm-wave transceivers is should be implemented in portable devices; thus, a highly integrated method is desirable to minimize package form factor. Owing to the high-level integration in CMOS, designs of wireless transceivers using CMOS technology have been in the spotlight.

A power amplifier (PA) is a circuit in the final stage of the wireless transceiver. The input signal should be amplified to ensure a long transmission range. 5G NR signals typically have a wide bandwidth and high peak-to-average power ratio (PAPR). Thus, to satisfy linear specifications such as EVM and ACPR with these signals, PA should operate in a large back-off region from the saturated output power. The output power satisfying the linear requirements decreases.

## a. Corresponding author; olee@pusan.ac.kr

Manuscript Received Jul. 13, 2022, Revised Aug. 29, 2022, Accepted Sep. 01, 2022

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (<a href="http://creativecommons.org/licenses/bync/3.0">http://creativecommons.org/licenses/bync/3.0</a>) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

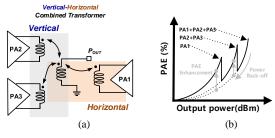

Fig. 1. (a) Block diagram of the proposed mm-wave multi-mode PA with vertical-horizontal combined transformer, (b) PAE versus output power with a using vertical-horizontal combined transformer

With the power combining method, the saturated output power and the linear output power can be increased. Among the power combining structures, transformer-based power combining methods have been widely used for fully integrated designs [1]-[13], [16]-[21]. Because the primary and secondary windings are spatially separated, the dc current flows only through the primary winding. Additionally, integrated transformers typically provide a balun function that converts differential signals into single-ended signal at the final output load.

Among the output combining transformer-based PA, series power-combining transformers (SCTs) and parallel power-combining transformers (PCTs) have been widely used [9]-[14], [19], [20], [22]-[24]. Compared to the SCT configuration, the PCT can be integrated into a relatively smaller area. Furthermore, there are imbalance problems in the input impedance provided by the SCT owing to the parasitic capacitance between the primary and secondary windings. For the construction of the PCT in few gigahertz range, the multi-turn secondary winding has typically been used and multiple primary windings interwind with the secondary winding in a lateral configuration [20], [21]. However, because a multi-turn secondary winding causes low Q and provides non-optimal low impedance to the power device in the mm-wave frequency range, the two primary windings cannot be interwound in a lateral configuration. In [17], two primary windings are placed below and above the one-turn secondary winding to form a two-input PCT configuration. Compared with previous PCT structure, a vertical-horizontal combining structure is adapted in the proposed structure. In this structure, three primary windings are placed horizontally and vertically to form a three-input PCT configuration. Compared with typical dual-mode PAs, the proposed architecture provides triple-mode operation (low, middle, high power modes).

Fig. 2. (a) Exemplary layout of the proposed power combining network, (b) simulated insertion loss of proposed power combiner

(b)

Frequency (GHz)

35

40

15

20

On the other hand, PA is one of the major power consumers in 5G mm-wave transceivers. To increase the battery usage time of portable devices, PA should operate efficiently. PA operates more probably in the low-output-power range than in high-output-power range [25]. Thus, the multi-mode PA, which operates with lower current consumption than the single-mode PA in the low-output-power region, has been studied [20]-[23]. Multi-mode operation is advantageous for extending the battery usage time of portable devices. In this work, a multi-mode PA with the proposed transformer is introduced to reduce the current consumption in low-output-power range. Three individual power amplifiers connected to the three primary windings are operated based on the mode change.

In this paper, we propose a fully integrated triple-mode Ka-band PA with vertical-horizontal combined transformer for 5G NR applications to improve the efficiency performance in the LP and MP modes with a compact size.

In Section II, a detailed description of the proposed power combiner and an explanation of the two-stage CMOS PA design are presented. The post-layout simulation results are presented in Section III. Finally, Section IV presents the conclusions of this work.

|                  | Driver stage (DA) | Power stage (PA) |

|------------------|-------------------|------------------|

| Supply VDD (V)   | 1.2               | 2.4              |

| Gate width (岬)/  | M5 – M6           | M1 – M4          |

| Gate length (nm) | 32/65             | 64/65            |

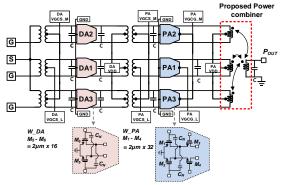

Fig. 3. Detailed schematic of the two-stage CMOS PA with proposed power combiner

# II. DESIGN OF THE PROPOSED POWER COMBINER AND KABAND POWER AMPLIFIER DESIGN

# A. Proposed parallel power combiner using verticalhorizontal combined transformer

The circuit diagram of the triple-mode PA using the proposed vertical-horizontal transformer is shown in Fig. 1(a). The proposed transformer is a parallel-power combining transformer with three inputs. In the proposed transformer, PA1 is connected to primary1, which is placed horizontally. Primary2 and primary3 which are connected to PA2 and PA3 are placed vertically down and up, respectively. Each primary winding is magnetically coupled to a secondary winding.

In LP mode, only PA1 is turned on and the other PAs are turned off. In MP mode, both PA2 and PA3 are turned on and PA1 is turned off. The HP mode requires all PA (PA1 + PA2 + PA3) to be turned on. Fig. 1(b) shows the PAE enhancement in the back-off region when using multi-mode PA.

Fig. 2(a) shows an exemplary layout configuration of the proposed vertical-horizontal combined transformer with 65-nm bulk CMOS technology. To construct the proposed vertical-horizontal transformer, 1.4μm thick aluminum pad (AP) layer, 3.4μm thick M8 copper layer, and 0.7μm thick M7 copper layer are used. As indicated by the red dotted box, primary1 and secondary windings use the same M8 layer to provide horizontal configuration. The primary1 is placed outside the secondary winding. Considering the connection of the output PAD and ground from the secondary winding, part of primary1 uses the M7 layer in the overlap area. The gray dotted box in Fig. 2(a) shows the vertical combination of the primary winding connected to PA2 and PA3. Unlike primary1, primary2 and primary3 are vertically placed below and above the secondary winding, respectively. The

M7 layer is used for primary2 and the AP layer for primary3. Using a compact vertical-horizontal combined transformer, it is possible to make a power combining transformer smaller in size, compared with previously studied power combining structures [20], [21]. Additionally, the proposed power combiner reduces current consumption in the MP and LP modes. Thus, it can be operated more efficiently if the PA should operate at a low-output-power level. The metal width of the three primary windings and secondary winding is  $8\mu$ m and the spacing between the two M8 metals for the horizontal structure is  $2\mu$ m. The size of the proposed transformer is  $660\mu$ m ×  $755\mu$ m.

To investigate the insertion loss performance of the proposed transformer, an ADS electromagnetic (EM) simulation was performed. Fig. 2(b) shows the simulated insertion loss of the proposed vertical-horizontal combined transformer. In the HP mode, the insertion loss is 0.54 dB at the targeted frequency 28 GHz. The insertion losses in the MP and LP modes are 0.56 dB and 0.98 dB at 28 GHz, respectively. The proposed transformer provides low-loss performance and the insertion losses are less than 1 dB for all three cases.

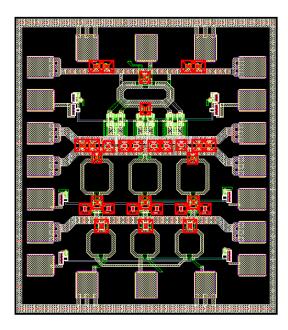

Fig. 4. Layout photograph of the proposed CMOS PA

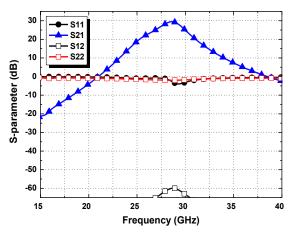

Fig. 5. Simulated small-signal S-parameters

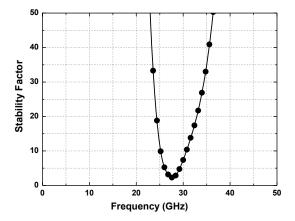

Fig. 6. Simulated stability factor

# B. Design of Ka-band CMOS PA

Fig. 3 shows a schematic of the proposed triple-mode PA with a vertical-horizontal combined transformer. The schematic consists of a two-stage configuration as input transformers, inter-stage transformers, and the proposed parallel power combining transformer. The driver stage (DA) is used to provide a sufficient gain for the overall power amplifier. Three power stages (PA1, PA2, and PA3) and three driver stages (DA1, DA2, and DA3) are operated based on the multi-mode operation.

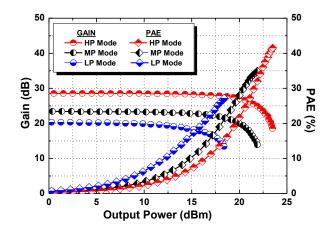

Fig. 7. Simulated gain and PAE versus output power in triple-mode at  $28\,\mathrm{GHz}$

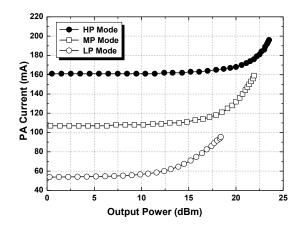

Fig. 8. Simulated current consumption of PA stages in triple-mode

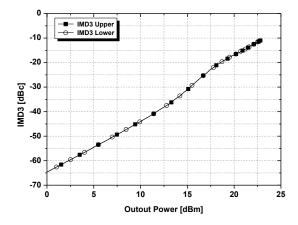

Fig. 9. Simulated IMD3

The bias conditions of PA2 and PA3 which operate in the MP mode, are the same (CS gate bias: PA VGCS\_M and CG gate bias: PA VGCG\_M). The bias of PA1 that operates in the LP mode is applied with the CS gate bias of PA VGCS\_L and CG gate bias of PA VGCG\_L. Similar to the bias conditions of the PAs, the gate bias of DA2 and DA3 are applied with DA VGCS\_M, while the gate bias of DA1 is applied with DA VGCS\_L.

For the configuration of the power stages, a cascode topology is applied with 2.4-V supply voltage. The device size of the common-source (CS) and common-gate (CG) devices is W/L =  $128\mu$ m /65 nm in M1, M2, M3, and M4, respectively. For the configuration of the driver stages, CS topology is applied with 1.2-V supply voltage. The W/L size of M5 and M6 is  $64\mu$ m /65 nm.

## III. POST-LAYOUT SIMULATION RESULTS

The proposed PA with a vertical-horizontal parallel power combiner was designed using 65 nm CMOS technology. The layout of the designed PA is shown in Fig. 4. The total chip size is  $660 \times 755 \mu \text{m}^2$ , including the dc supply pads and ground pads. Furthermore, the chip does not require additional off-chip matching because it includes input and output matching networks.

The simulated S-parameter results are shown in Fig. 5. S21 shows that the gain of PA is 28.5 dB at 28 GHz. Fig. 6 shows that the simulated stability factor is greater than one from 15 GHz to 40 GHz. The 1-tone simulation results for the PA with the proposed output power combiner are shown in Fig. 7. The simulated power gains of the proposed multimode PA are 20.3, 23.4, and 28.5 dB in LP, MP, and HP modes, respectively. The saturated output power,  $P_{\rm SAT}$ , are 18.4, 21.9, and 23.5 dBm with peak PAE, PAE<sub>peak</sub>, of 27.2, 34.9, and 41.5% in the LP, MP, and HP modes, respectively. The PAE results for each mode included the power consumption of the DA stages.

Fig. 8. shows the current consumption of the PA stages in triple-mode versus the output power at 28 GHz. When PA operates in the MP mode, the current consumption improved by 27.1% at 18.5 dBm output power, e.g. 5-dB back-off, when compared to the operation in the HP mode. The PA current at 18.5 dBm output power reduced from 166 mA in the HP mode to 121 mA in the MP mode. Compared to the

HP and LP modes at a 13.5 dBm output power, e.g. 10-dB back-off region, the current consumption of the proposed triple-mode PA improved by 61.1% because the PA current decreased from 162 mA to 63 mA.

Therefore, thanks to the proposed vertical-horizontal combined transformer provides low insertion loss in a small size, the PA with the proposed transformer can achieve a high  $P_{\text{SAT}}$  of more than 23 dBm and PAE<sub>peak</sub> of 41.5%. The IMD3 results are shown in Fig. 9.

Table I presents a comparison with other reported fully integrated 5G CMOS PAs in the mm-wave band. The proposed fully integrated triple-mode PA achieves not only a high  $P_{\rm SAT}$  and PAE<sub>peak</sub> in the HP mode but also the highest PAE in both the 5-and 10-dB back-off regions, PAE<sub>5dB</sub> and PAE<sub>10dB</sub>. A figure of merit (FOM) represents overall performance of the PA. The proposed PA shows the highest FOM among the previously reported KA-band CMOS PAs in table I.

TABLE I. Comparison of the proposed PA with the reported Ka-band CMOS PAs.

|                           | This<br>Work <sup>#</sup> | [16] | [17] | [18]  |

|---------------------------|---------------------------|------|------|-------|

| Tech. (nm)                | 65                        | 65   | 65   | 65    |

| Freq. (GHz)               | 28                        | 28   | 28   | 28    |

| Gain<br>(dB)              | 28.5                      | 18   | 15.9 | 15.8  |

| $P_{\mathrm{SAT}}$ (dBm)  | 23.5                      | 18.5 | 23.2 | 15.6  |

| $P_{ m O,1dB}$ (dBm)      | 19.4                      | 17*  | 22   | 14    |

| PAE <sub>peak</sub> (%)   | 41.5                      | 27.3 | 33   | 41    |

| PAE <sub>5dB</sub><br>(%) | 21.5                      | 15*  | 18*  | 18*   |

| PAE <sub>10dB</sub> (%)   | 13                        | 12*  | 8*   | 7*    |

| FOM                       | 97.1                      | 79.8 | 83.2 | 76.4  |

| Chip size (mm²)           | 0.49                      | 0.45 | 0.78 | 0.35* |

$FOM = P_{sat} (dBm) + Gain (dB) + 10log(PAE[\%] \times f^{2}[GHz])$  #Simulated results

# IV. CONCLUSION

This paper has proposed a triple-mode CMOS PA with a vertical-horizontal parallel-combined transformer using 65 nm CMOS technology. Using the proposed power combiner with a compact size, the triple-mode PA achieves improved efficiency performance with low-current consumption in the middle- and low-output-power regions. The triple-mode PA shows decreased current consumption of 166 mA to 121 mA (HP mode versus MP mode) at 18.5 dBm, e.g. 5-dB back-off, and 162 mA to 63 mA (HP mode versus LP mode) at 13.5 dBm, e.g. 10-dB back-off. Additionally, the proposed PA achieves a 23.5-dBm  $P_{\rm SAT}$  and 41.5% PAE<sub>peak</sub> in the HP mode.

<sup>\*</sup>Graphically estimated.

#### ACKNOWLEDGMENT

This work was supported by the National Research Foundation of Korea(NRF) grant funded by the Korea government(MSIT) (NRF2020R1A2B5B01001508).

This work was supported by the MSIT(Ministry of Science and ICT), Korea, under the ITRC(Information Technology Research Center) support program(IITP-2022-2017-0-01635) supervised by the IITP(Institute for Information & communications Technology Promotion).

The chip fabrication and CAD tools were supported by the IDEC, Korea.

## REFERENCES

- [1] M. Thian et al., "A 76–84 GHz SiGe power amplifier array employing low-loss fourway differential combining transformer," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 2, pp. 931–938, Feb. 2013.

- [2] J.-W. Lai and V.-G. Alberto, "A 1V 17.9dBm 60GHz power amplifier in standard 65nm CMOS," *in Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp.424-425, 7-11 Feb. 2010.

- [3] M. Bohsali and A. M. Niknejad, "Current combining 60 GHz CMOS power amplifiers," *in Proc. IEEE Radio Freq. Integr. Circuits Symp.*, pp. 31–34, May 2009.

- [4] G. J. Gu et al., "Two-way current-combining W-band power amplifier in 65-nm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 5, pp. 1365–1374, May 2012.

- [5] C.-W. Tseng and Y.-J. Wang, "A 60 GHz 19.6 dBm power amplifier with 18.3% PAE in 40 nm CMOS," *IEEE Microw. Wireless Compon. Lett.*, vol. 25, no. 2, pp. 121–123, Feb. 2015.

- [6] J. Xia et al., "60-GHz power amplifier in 45-nm SOI-CMOS using stacked transformer-based parallel power combiner," *IEEE Microw. Wireless Compon. Lett.*, vol. 28, no. 8, pp. 711–713, Aug. 2018.

- [7] J. Oh et al., "A 77-GHz CMOS power amplifier with a parallel power combiner based on transmission-line transformer," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 7, pp. 2662–2669, Jul. 2013.

- [8] M. Nariman et al., "A compact 60-GHz wireless power transfer system," *IEEE Trans. Microwave Theory Tech.*, vol. 64, no. 8, pp. 2664–2677, Aug. 2016.

- [9] E. Kaymaksut et al., "Transformer-based doherty power amplifiers for mm-wave applications in 40-nm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 4, pp. 1186–1192, Apr. 2015.

- [10] D. Zhao and P. Reynaert, "A 0.9V 20.9dBm 22.3%-PAE E-band power amplifier with broadband parallel-series power combiner in 40nm CMOS," in Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, pp.248-249, Feb. 2014.

- [11] Y. Zhao and J. Long, "A wideband, dual-path, millimeter-wave power amplifier with 20 dBm output power and PAE above 15% in 130 nm SiGe-BiCMOS," *IEEE J. Solid-State Circuits*, vol. 47, no. 9, pp. 1981– 1997, Sep. 2012.

- [12] U. Pfeiffer and D. Goren, "A 23-dBm 60-GHz distributed active transformer in a silicon process technology," *IEEE Trans. Microw. Theory Techn.*, vol.

- 55, no. 5, pp. 857–865, May 2007.

- [13] Y.-N. Jen et al., "Design and analysis of a 55–71-GHz compact and broadband distributed active transformer power amplifier in 90-nm CMOS process," *IEEE Trans. Microw. Theory Tech.*, vol. 57, no. 7, pp. 1637–1646, Jul. 2009.

- [14] D. Zhao and P. Reynaert, "A 60-GHz dual-mode class AB power amplifier in 40-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 48, no. 10, pp. 2323–2337, Oct. 2013.

- [15] C. Kim et al., "A 28-GHz CMOS down-conversion mixer with low-magnetic-coupled source degeneration inductors for 5G applications," *Journal of Semiconductor Technology and Science*, vol. 19, no. 4, pp. 373-377, Aug. 2019.

- [16] S. Lee et al., "A 28-GHz CMOS linear power amplifier with low output phase variation over dual power modes," in *IEEE Microwave and Wireless Components Letters*, vol. 29, no. 8, pp. 551-553, Aug. 2019.

- [17] H. Ahn et al., "A 28-GHz highly efficient CMOS power amplifier using a compact symmetrical 8-way parallel-parallel power combiner with IMD3 cancellation method," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), pp. 187–190 Aug. 2020.

- [18] S. N. Ali et al., "A 28GHz 41%-PAE linear CMOS power amplifier using a transformer-based AM-PM distortion-correction technique for 5G phased arrays," 2018 IEEE International Solid State Circuits Conference (ISSCC), pp. 406-408, Feb. 2018.

- [19] K. H. An et al., "Power-combining transformer techniques for fully-integrated CMOS power amplifiers," *IEEE J. Solid-State Circuits*, vol. 43, no. 5, pp. 1064– 1075, May 2008.

- [20] H. Ahn et al., "Fully-integrated WLAN CMOS PA with reconfigurable transformer," in *Electronics Letters*, vol. 54, no. 9, pp. 574-576, May. 2018.

- [21] H. Ahn et al., "A fully integrated dual-mode CMOS power amplifier with an autotransformer-based parallel combining transformer," in *IEEE Microwave and Wireless Components Letters*, vol. 27, no. 9, pp. 833-835, Sep. 2017.

- [22] J. Kim et al., "A linear multi-mode CMOS power amplifier with discrete resizing and concurrent power combining structure," *IEEE J. Solid-State Circuits*, vol. 46, no. 5, pp. 1034–1048, May 2011.

- [23] K. H. An et al., "A 2.4 GHz fully integrated linear CMOS power amplifier with discrete power control," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 7, pp. 479–481, Jul. 2009.

- [24] E. Kaymaksut and P. Reynaert, "dual-mode CMOS doherty LTE power amplifier with symmetric hybrid transformer," in *IEEE Journal of Solid-State Circuits*, vol. 50, no. 9, pp. 1974-1987, Sep. 2015.

- [25] T. Fowler et al., "Efficiency improvement techniques at lower power levels for linear CDMA and WCDMA power amplifier," in *Proc. IEEE RFIC Symp.*, Jun. 2002, pp. 41–44.

application.

Geun Tae Kim received the B.S. degree in Electrical Engineering from Pusan National University, Busan, Korea, in 2017, and is currently working toward M.S. degree in electrical engineering at Pusan National University, Busan, Korea.

His interest includes mm-wave power amplifier design for mobile

**Kyu Taek Oh** received the B.S. degree in Electrical Engineering from Pusan National University, Busan, Korea, in 2017, and is currently working toward M.S. degree in electrical engineering at Pusan National University, Busan, Korea.

His interests include mm-wave power amplifier design for mobile

applications and DC-DC converters.

**Hyun Jin Ahn** received the B.S. and the Ph.D. degrees in electrical engineering from Pusan National University, Busan, South Korea, in 2015 and 2021, respectively.

He was an Intern with Qualcomm Inc., San Diego, CA, USA, where he was involved in the development of power amplifier (PA) and passive circuits for 5G applications. Since 2022, he has been with Qualcomm

Inc., San Diego, CA, USA, where he is involved in designing the PA and passive circuits for 5G applications. His interests include high-frequency power amplifier design for mobile applications and low power circuit design.

Ock Goo Lee received the B.S. degree in electrical engineering from Sungkyunkwan University, Korea, in 2001, the M.S. degree in electrical engineering from the KAIST, Korea, in 2005, and the Ph.D. degree in electrical and computer engineering from the Georgia Institute of Technology, USA, in 2009.

Upon completion of the doctoral degree, he joined Qualcomm Inc., USA, as a Senior Engineer, where he was involved in the development of transmitters and integrated passive circuits on mobile applications. He is currently a faculty member with the Department of Electrical Engineering, Pusan National University, Korea. His research interests include high-frequency integrated circuits and system design for wireless communications.